# 第一章 整机概述

PDP403 型等离子电视是 TCL 王牌电子有限公司开发、生产的高科技产品,它融合了电视技术、计算机显示技术、等离子显示技术等多门类科学,代表了电视机"大屏幕、高清晰、平板化、信息化"的发展潮流。

PDP403 由等离子显示屏(Plasma Display Panel,简称 PDP)、分立音箱和控制盒构成,具有模拟电视接收显示功能,将隔行扫描的电视信号转为逐行扫描信号,画面细腻、清晰,不闪烁,可接驳传统的视听设备如 DVD、VCD、录象机等;还具有电脑、SDTV显示功能;可连接电脑主机、逐行 DVD、SDTV 机顶盒等;音质优美,高音清晰,中音明快,低音丰富,是家庭影院视听设备的理想选择。

#### PDP403 主要功能特点如下:

#### 一、超薄等离子显示屏

该产品采用了具有国际先进水平的等离子显示技术,屏幕大,机身薄,整机厚度仅为7.8cm。平板数字显示,物理分辨率为640×480,清晰度高,且边角和中心的清晰度完全一致,画面重现力强,彩色鲜艳,图象无失真、变形,具有高亮度和高对比度、宽视角、低辐射、抗电磁干扰等特点。

#### 二、60Hz逐行扫描精密显像

采用先进的数字化处理技术,将现有的 50Hz 隔行扫描信号转为 60Hz 逐行扫描信号,彻底消除了普通电视存在的大面积闪烁、行间闪烁、行抖动、行结构线等固有缺陷,画面细腻、清晰,不闪烁,另外,还具有动态降噪功能,有效滤除画面噪点。

#### 三、电脑显示功能

具有标准 VGA 接口,可连接电脑主机,作为大屏幕显示器,对比度、亮度高,彩色鲜艳,显示游戏、影视画面效果好,支持格式从640×480/60HZ~1024×768/85Hz。

#### 四、丰富的输入输出接口

本机具有天线输入接口,一路 DVD 分量 YCbCr 接口,两路 AV 输入接口(其中 Video1 与分量 Y 输入共用),两路 S 端子输入接口,一路 AV 输出接口,VGA 接口除了接电脑主机外,还可接逐行 DVD,SDTV 机顶盒等,并具有外界扬声器端子,是家庭影院系统理想的终端显示和声音重放设备。

#### 五、多种画质改善电路

采用双制式数字梳状滤波器,有效滤除亮色串扰;有亮度、色度动态改善电路(LTI、CTI),提升轮廓清晰度;并有动态蓝、黑电平扩展,绿色增强,肤色校正、 y 校正等功能,大幅度提升画质,画面透亮度高,肤色自然,彩色鲜艳、逼真。

#### 六、 数字音效处理电路

采用全新的伴音数字处理电路,具有全球通丽音功能,支持双语言、立体声,并具有五段均衡调节、动态低音增强、环绕音效,智能音量控制等多种功能,已设置四种固定音效模式:标准、音乐、新闻、环绕,用户也可随意调节五段均衡,系统会自动保存为个人设置。七、全频段、多制式接收功能

100 个频道,可接收全频段的电视节目,使用锁相环路频率合成高频头,搜台快速、准确;天线输入端可接收、处理 PAL-D/K、PAL-I、SECAM-D/K、SECAM-I 制电视信号,AV输入可处理 PAL、NTSC、SECAM 制彩色电视信号。

#### PDP403 整机维修的一般原则:

- 一、根据故障表现判断故障点组件:

- 1,PDP403机顶盒上CPU为核心,开机时要检测显示屏是否正常,包括硬件检测和软件通讯协议,屏上接口电路异常或电源(PSU)失败,都会导致不开机,机顶盒蓝灯闪烁几秒后又变为红灯。此时需检查25针连线接口是否松动,机顶盒数字处理板CPU复位脚电压是否正确,屏上LVDS转接板控制电路是否虚焊、假焊,显示屏电源电压是否正常。

- 2, 画面出现规则的大面积黑块(约占整屏 1/4)、或彩色细长条等规则缺陷,可能是地址驱动电路接口线插松动或损坏、柔性电路划伤或其上某条印刷线路烧断。

- 3,开机正常,但画面不亮,须检查显示屏电源扫描电压Vsc、维持电压Vs、地址驱动电压Va是否正常,若其中一路异常,须断开与驱动板相连的有关线插,确认是电源问题还是驱动电路损坏。(电源的调节和检测详见电源部分的介绍)

#### 注意: 插拔线插之前一定要做好对应标记, 以免误插损坏显示屏。

- **4**, 开机正常, 无画面, 但有背景亮光且按菜单键有显示, 须检查机顶盒工厂设定有关逐行处理部分数据是否正常, 此部分电路供电电压是否正常。

- 5, 画面大部分正常,但某些画面或边缘随机出现不规则彩色点状干扰或彩斑,或感觉缺某种色,首先检查 25 针连线是否松动,然后检查 A/D 转换、数字处理部分 IC 是否连焊、虚焊或有异物,再更换显示屏上 41 针 R、G、B 数据连线。

- 6,显示屏上的缺陷点,由于目前制造工艺的限制,很难避免。对 40 时而言,有两个以内的不连续缺陷点属正常情况,不应作为坏机处理。

#### 二、PDP403故障处理办法

如果可能的话,请用相机拍下故障情况,并记下显示屏左上脚的显示模块编号(供应商 器件编号)。

- 1,显示屏故障

- A 驱动电路损坏,可换板解决的,寄回总部维修驱动板。

- B 柔性电路损坏及不可维修时再将整机寄回总部。

- **2**,显示屏电源故障,一般不建议维修,寄回总部或用备损件更换,除非是明显的简单故障。

- **3**, 机顶盒故障,可先用好机顶盒确认,再查是哪块板,更换或维修,根据紧急程度处理。

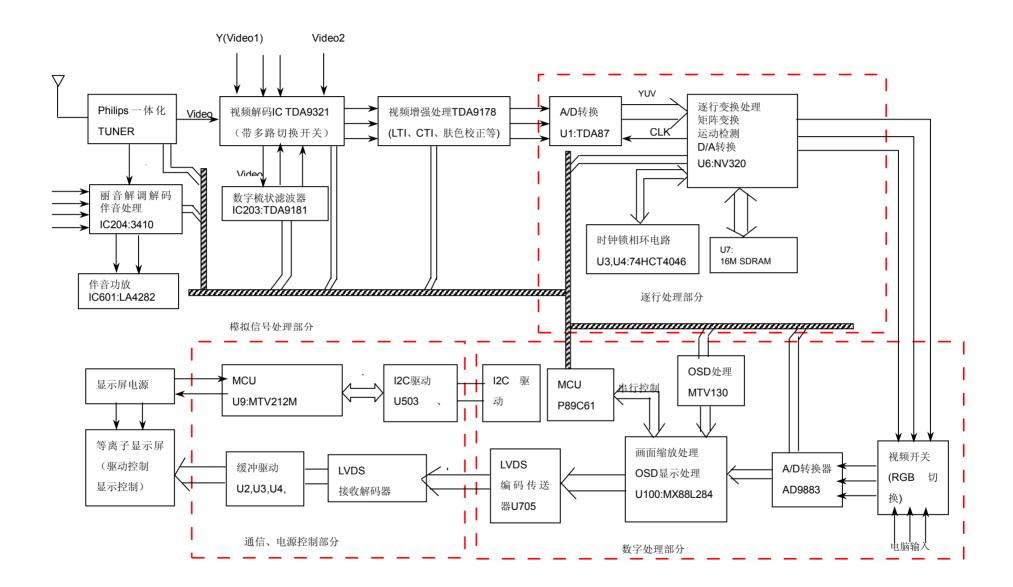

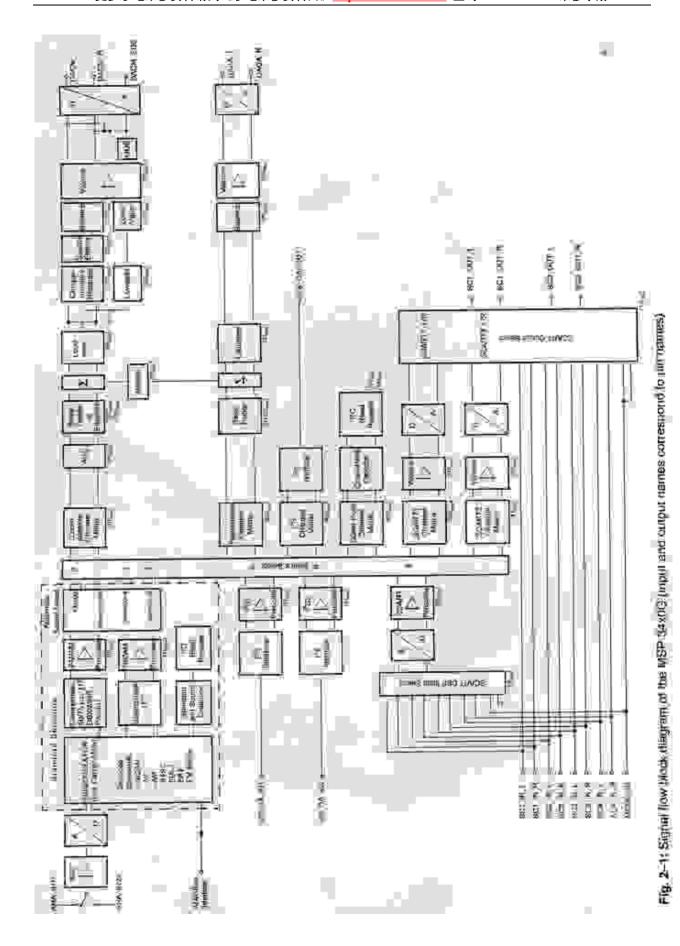

下页为 PDP403 的整机信号流程图,包括模拟处理部分、逐行处理部分、数字处理部分和通信与电源控制部分。

# 第二章等离子显示屏

## 第一节 等离子显示原理

等离子显示屏的屏体主体上是由相距几百微米的两块玻璃板组成,与空气隔离,其中注入 Ne、Ar、Xe 等惰性气体,以 Ne 为主,Ar、Xe 较少,气压在 500~600Torr(0.7 个大气压)左右,每块玻璃板都有各自的电极。

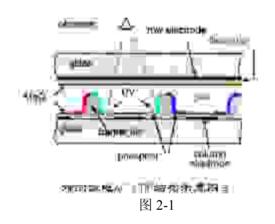

PDP 按工作方式可分为 DC-PDP 和 AC-PDP 两种基本类型,DCPDP 电极和气体直接接触,ACPDP 则在电极上涂敷介电层。AC-PDP 从结构上又可分为双基板和单基板两类,双基板的维持电极正交分布在两个基板,放电发生在两基板之间,又称为对向放电型;单基板的维持电极在同一基板上,放电发生在单一基板表面,又称表面放电型。图 2-1 是对向放电型 AC-PDP 的结构示意图。

交流 PDP 的特殊性就在于它的电介质层,能够使电荷在其表面聚集形成壁电压。壁电压与外加电压相加减,从而改变气体上的电压。当两板之间的电压刚刚低于点火电压时,有壁电压的单元就会击穿放电。放电能够将电荷从一个电极移向配对电极,从而帮助反向电压周期的放电,于是放电将会连续进行下去。交流 PDP 的这种能保持同一放电状态的特性叫做"记忆功能"。关闭单元时使用窄脉冲,使电荷来不及转移,从而使放电无法维持。

对单个单元来说,存在点火电压与最小维持电压的"记忆裕量";而对整个显示屏来说,存在着最先开通电压和最后关断电压。对与 PDP 的维持电压来说,应低于最先开通电压,高于最后关断电压。其间的范围大小表征了显示屏的均匀性。

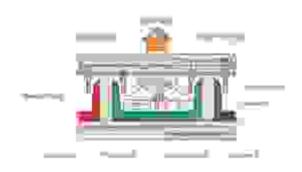

目前的 PDP 多采用三电极表面放电的工作方式,其单元结构如图 2-2 所示。从上到下依此为前侧玻璃基板、扫描电极 X(Scan)、保持电极 Y(Sustain)、介电层、保护层(MgO)、RGB 磷光粉、隔离墙、地址电极(Address)和后侧基板。

其中上基板的电极由一个宽的透明 ITO 电极和一个窄的总线电极(铬铜铬)组成,MgO 保护层;下基板采用印刷银电极,涂介质。AC PDP 中广泛使用 MgO 作为放电介质的保护层,主要是因为其二次电子发射系数大,耐离子轰击性能好的缘故;另外还可以起到保持放电位置的作用。

图 2-2

驱动方法从原理可以分为两类:寻址/显示异步 ADS 方式和寻址/显示同步 AWD 方式。寻址/显示异步方式包含了子场和独立的寻址周期和复位周期,PDP 的灰度可以通过该方式来实现,同时可简化驱动并实现较宽的工作范围和稳定的工作状态。而寻址/显示同步 ADS 方式虽然也有子场的概念,但没有分开的寻址周期和复位周期,驱动电路复杂,工作范围小。

等离子体显示屏是以等离子体显示平板(Plasma Display Panel,简称 PDP)为显示器件的大屏幕显示系统,它是以惰性气体在真空中放电而产生紫外线来激发红、绿、蓝荧光粉,形成彩色显示。

#### 1, 可见光的产生:

一般情况下,PDP 是利用 1%-10%Xe 与 Ne 或 He 混合气体的潘宁效应(Penning effect)来降低点火电压,在电场的作用下发生辉光放电(glow discharge);在放电过程中,电子与 Xe 原子发生碰撞使其跃迁至激发态;激发态的 Xe 发射 147nm 真空紫外光(VUV)回到基态;同时 147nm 的紫外线激发荧光粉,使其发射出可见光。

图 2-3

#### 2,对向放电 AC PDP 的基本工作过程:

- (1) 维持电压 Vs 投入, 但 Vs<Vb(Breakdown Voltage), 辉光放电不能发生。

- (2) 写电压 Vwr 投入(寻址), Vwr+ Vs> Vb, 辉光放电发生, 输出光脉冲。

- (3) 辉光放电产生的壁电荷电压 Vw 与 Vs 叠加使辉光放电终止。

- (4) Vs 的另外半周与壁电荷电压 Vw 叠加使辉光放电再次发生。

- (4) (3) 循环进行使被寻址像元持续发光。

(5) 在 Vs 为 0 电平时用与 Vw 相反之擦除脉冲 Ve 即可消除壁电荷,从而使该像元熄灭。

特点: 记忆特性(Memory Mode),维持脉冲宽度一般为 5-10μs,频率为 30-50kHz,幅值为 90-100V。由于对向放电 AC PDP 在使用寿命、成品率等方面存在的问题,目前 PDP 的主流结构已逐渐转为三电极表面放电。

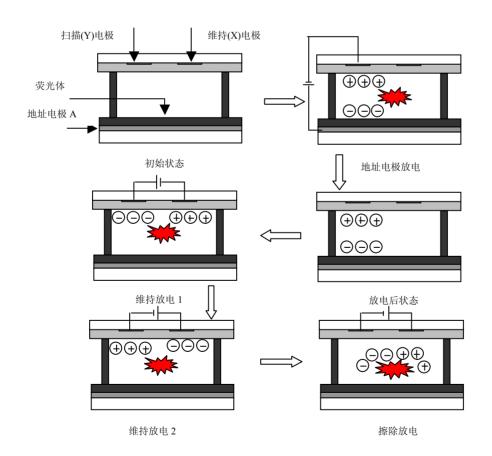

#### 3,三电极表面放电 AC PDP 的工作过程:

- (1)显示电极 X 与寻址电极 A 之间加大于着火电压的一脉冲写入电压,形成壁电荷。

- (2) 壁电荷电压与显示电极 X,Y 所加维持电压共同作用使被寻址像元持续发光。

- (3) 在显示电极 X,Y 加一适当幅值和脉宽之擦除电压,即可消除壁电荷,并使该像元熄灭。 具体过程如下图所示:

图 2-5

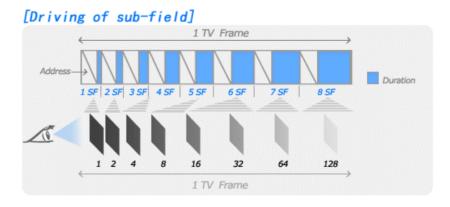

图 2-6 彩色 PDP 灰度控制示意图

在 PDP 中, 目前多采用分离子场 (Sub-field) 技术来实现灰度控制, 此项技术为日本富士通公司 在 1992 年提出。所谓子场就是将一帧图像的显示时间分成若干段来显示,每段的维持显示期之比为 1:2:4:8·····(其实是包含的同一频率的 Sustain Pulse 的数不同而使其辉度的相对值也不同),即 第 k 个子场发光时间是第 k+1 个子场发光时间的一半, 相应平均亮度也是后者的一半。现通常将一帧 图像分成8个子场,因此在一帧图像内可以实现256种亮度组合,即可以实现256级灰度控制。

在每一个子场中,包含着以下的几个工作过程:

- ∂ 全屏擦除:擦除上一子场形成的壁电荷

- 全屏写入: 形成全屏的壁电荷

- · 全屏擦除:擦除多余的壁电荷

- ≠ 寻址电极数据写入:逐行顺序扫描,使要放电的单元建立合适的壁电压

- 维持放电: X, Y 电极见加入交变电压, 有地址数据写入的单元持续放电

从以上过程可以看出,PDP 采用的是寻址与显示分离的技术(ADS): 先寻址,后显示,利用了 壁电荷不会自行消失的记忆效应。

PDP 的彩色显示是通过控制每个 R、G、B 放电单元累计放电时间的长短从而控制该单元的亮度, 并通过空间混色来实现的。对于 8 个子场,256 级灰度的控制模式来说可实现  $16777216(2^{24})$ 种颜色, 即我们平常所说的真彩色(见下图)。

第二节 驱动控制电路

PDP采用存储式驱动方式,大体由写入、发光维持、和擦除三个部分组成。驱动电路的作用是给PDP施加定时的、周期的脉冲电压和电流。 随着驱动电路极性的变化,电极表面介电层上周期性地蓄积、释放电荷,从而实现图像的显示。

驱动电路分几个部分,包括列驱动器、行驱动器、同步控制器、数据缓冲器。显示驱动都是通过在显示板行、列的各个电极上,选择性地施加较高的电压来进行的。

通常,驱动器内部分为两部分:一是逻辑电路,负责控制显示屏信号和处理显示数据;二是驱动电路,负责将信号电平移位和对显示屏施加发光所需的脉冲。

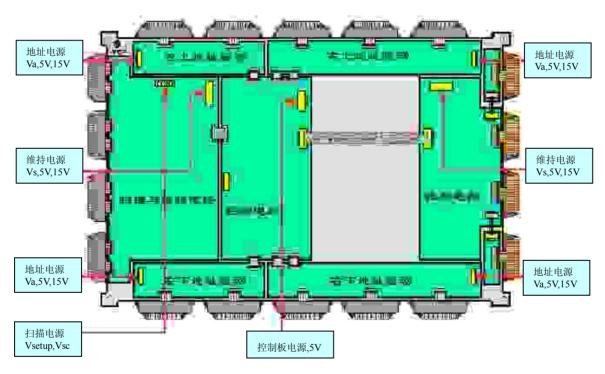

#### 一,驱动电路的布局:

PDP403 采用 LG 公司的第四代 40 吋等离子显示模块,型号为 PDP40NVDN4,比例为 4:3,分辨率为 640X480,扫描方式为双扫描。

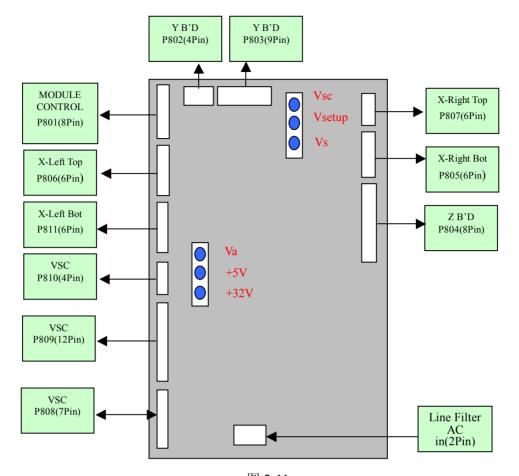

整个显示模块从背面看,包括控制电路、扫描与维持电路(Y 板)、维持电路(Z 板)和上下左右共四块地址驱动电路(X 板)。X 板和 Y 板通过邦定(bonding)电路,即芯片覆膜,和 FPC(Flexible Printed Circuit),即柔性印刷电路,与显示屏相连;各板之间的数据信号通过扁平排线相连。整个模块的电路分布如下图所示,相关的电源值也已标出。

图 2-8

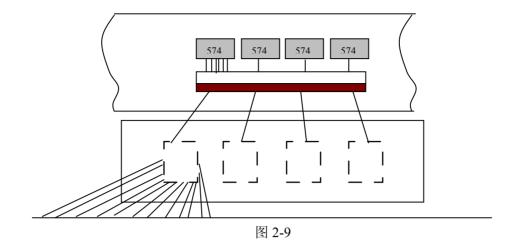

#### 二,地址驱动的分布:

为了完成 640 列 RGB 的地址驱动,共需要 640X3 路的电路。地址驱动所连接的柔性电路上下各分为 5 组,每组的地址信号经控制电路送出后,经过地址驱动电路上的 4 个 8 位 D 触发器(AC574,只用到其中的 6 位),将数据送往所连接的金属片下的颗绑定 IC 上 (COF)。每颗 IC 接收所对应的 574 送来的 6 位数据,通过 IC 内部的移位寄存器,将 16 个脉冲所带来的全部 96 个数据并行输出,控制相应的 96 列像素的显示。以上的关系,对判断不同类型竖线损坏的原因具有很重要的作用。具体情况见下图:

#### 三,扫描电路的分布:

480 行的扫描最终由模块左侧的 4 组电路来完成,每组电路上包含两颗绑定的行扫描驱动 IC。每颗 IC 接收来自扫描驱动板的有关信息,按顺序发出 60 路的扫描脉冲。在双扫描的方式下,扫描脉冲最先从上下两端的那一行开始,顺序向中间进行,当两边的两颗 IC 完成扫描后,下面的一颗 IC 才开始工作。因此,如果两头的 IC 有故障,将会影响到半屏的图像显示;而最中间的 IC 故障,只能影响到它本身所控制的那 60 行。对此的理解也有助于对行扫描方面的故障的判断。

PDP 电源一般不作为模块的组成部分,而是由整机厂自主制造或由电源供应商提供。 PDP 电源的主要特点:

宽交流电输入,功率因数调整率 PFC 要到 99%以上(根据 EN61000-3-2)

高的效率(在220V输入时要达到92%以上)

CLASS B 的传导和辐射标准 (EN55022)

输入电源符合环保要求(Blu angel, Energy star)

5V, 0.5A 辅助的待机 (STAND BY) 输出电压

具有遥控开关信号

无最小负载要求

受限制的尺寸, 高度在 30~40mm 左右

自然通风, 无风扇

要通过安全方面的认证(EN60950,UL1950,CSA22.2,IEC60950标准,CE认证)

PDP的电源担负着屏内所有电路和显示屏的供电,高压部分包括向驱动器提供维持电压(三电极表面放电约为55-65V)和扫描电压(165-185V),一般直接送入驱动电路板提供行列驱动电源。维持电压和扫描电压是在一定范围内动态变化的电压,该两组电压由控制电路反馈的两个信号分别控制;低压部分包括控制板、接口板等各部分的±5V 电路供电电压。电源同时还应具有针对屏故障的过压过流保护功能,为了保护显示屏和扫描电路,电源的时序受到严格的控制。PDP403 电源的输出功率约为350w。

下面介绍在 PDP403 上广泛使用的 EPTL40B 电源的工作原理:

#### 一、 概述:

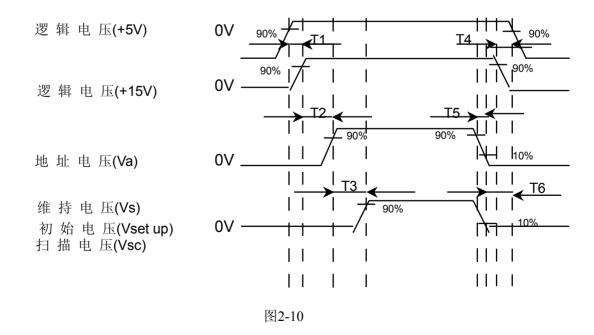

1, 该等离子电视机工作时,对电源要求有多组输出电压,精度要求高,故该电源采用多组芯片 控制模式,电路结构相对比较复杂,为满足电流谐波标准,该电源电路中有有源功率因素校 正电路,同时该电源要求较严格的工作时序。其工作时序如下:

#### 电源开关机时序

开机时序:  $+5V \rightarrow +15V \rightarrow Va \rightarrow Vs$ , Vset up, Vsc 关机时序: Vs, Vset up,  $Vsc \rightarrow Va \rightarrow +15V \rightarrow +5V$

注意:如果电源不遵循以上的工作时序框图,PDP驱动将会产生永久性的损伤。所以,AC电源输入以后,电源开关ON/OFF,必须遵循以上的工作时序。

#### 图中:

T1: Min 0 msec (From 90% of +5V voltage to 90% of +15V voltage time)

T2: Min 500 msec (From 90% of +15V voltage to 90% of Va voltage time)

T3: Min 200 msec (From 90% of Va voltage to 90% of Vs voltage time)

T4: Min 0 msec (From 90% of +15V voltage to 90% of +5V voltage time)

T5: Max 300 msec (From 90% of Va,Vs voltage to 10% of Va,Vs voltage time)

T6: Min 20 msec (From 10% of Va, Vs voltage to 90% of +5V voltage time)

Note: T4 and T5的工作时序不是强制执行的。

#### 2. 各主要输出电压规格:

| 项 目   | 符号      | 条件   | 最小值  | 最大值 | 单 位 |

|-------|---------|------|------|-----|-----|

| 逻辑电压  | Vcc     | 25°C | 4.5  | 6   | V   |

| 逻辑电压  | +15V    | 25°C | 13.5 | 16  | V   |

| 地址电压  | Va      | 25°C |      | 80  | V   |

| 维持电压  | Vs      | 25°C |      | 195 | V   |

| 初始化电压 | Vset up | 25°C |      | 250 | V   |

| 扫描电压  | Vsc     | 25°C |      | 115 | V   |

3. 该电源由输入电路、+5Vsb 电路、AC OK 电路、继电器控制电路、+32V 电路、+19V、+15V、+12V 低压输出电路、+5V 电路、PFC 电路、Va 电路、Vs 电路、Vset-up 电路、Vsc 电路构成,下面就各电路作一简单介绍。

# 二、输入电路:

该电路主要的功能是输入噪声滤波,C2、L1、L2组成共模输入,C1、C4组成差模输入。共模输入电路作用,一方面滤除高频信号对电源的干扰,另一方面防止电源产生的高频信号对电网的污染。差模输入电路主要起滤除高频杂波信号的作用;主电源整流滤波电路由 B1、C3组成;+5Vsb整流滤波电路由 B2、C16组成;R5是压敏电阻器,起抑制尖峰电压作用;R19是NTC热敏电阻,主要是防止浪涌电流对电路的冲击。

#### 三、5Vsb 电路:

该电路主要是由 UC3843 等元件构成降压反激式变换器,输出+5V 和+15V 的辅助电压; UC3843 是 PWM 控制器,各引脚功能如下:

| 引脚 | 功能         | 引脚 | 功能         |

|----|------------|----|------------|

| 1  | COMP 比较器输出 | 5  | GND 地      |

| 2  | VFB 比较器输入  | 6  | GDPWM 信号驱动 |

| 3  | IS 电流测定    | 7  | VCC 电压供应   |

| 4  | RT/CT 振荡   | 8  | VREF 电压基准  |

R20、C13、D7 向 UC3843 提供启动电压,D8、C12 整流滤波输出+15V 的辅助电压,供给 UC3843、LM358 等控制电路工作电压;Q1、T1 等组成开关电路,T1 耦合供应输出能量,D6、C10、R16 吸收Q1 反向尖峰电压;D5、C14、C17 输出整流滤波,产生+5Vsb 电压输出;R22、R29 是输出电压取样电阻,其取样信号控制U7,U7 输出经U6 光电隔离耦合,回授给U5的第 1 脚。同时R131 取样电流信号经R27、C20 耦合给U5的第 3 脚。共同调整第 6 脚的输出占空比。

#### 四、AC OK 电路:

由 LM358 组成窗口比较器,当输入 AC 电压在设定的  $170V^2$ 265V 工作范围之内时,AC OK 输 高电平信号,否则输出低电平;其中 R9、R8、C5 分压产生 LM358 第 3 脚的基准电压,R7、R12、R15 采样 AC 输入电压,调整 R12,当输入电压低于 170V 时, $U_{IA}$  第 2 脚低于第 3 脚电压,第 1 脚就输出高电平,经 U4 (LF038) 耦合,AC OK 输出低电平,否则,当输入电压高于 170V 时, $U_{IA}$  输出低电平,不影响  $U_{IB}$  的输出;同样,R14、C8 产生  $U_{IB}$  的基准电压输入  $U_{IB}$  的第 6 脚,R6、R10、R16 组成采样电路,输入第 5 脚,调整 R10,当输入电压高于 265V 时, $U_{IB}$  第 6 脚低于第 5 脚,第 7 脚就输出高电平,ACOK 输出低电平,当输入电压低于 265V 时, $U_{IB}$  输出低电平也不影响  $U_{IA}$  的输出; D3、D4 组成  $U_{IA}$ 、 $U_{IB}$  输出"或"的关系

#### 五、继电器控制电路:

由 U9 (LF038)、Q2、U8 (TL431)、K1、K2 等元件组成。当 "Remote\_control"端输入+5V 控制信号,U9 耦合使 Q2 导通,K1 加电吸合,市电经 K1、R1~R3、B1 向 C 50、C51、C52 充电,R1~R3 防止浪涌电流对主电路冲击; K1 吸合的同时,Q2 输出电压通过 R36 向 C24、R35 向 C23 充电,延时一段时间,U8 加电导通,K2 吸合,使市电通过 K1、K2 直接向 B1、C50、C51、C52 供电;

#### 六、+32V 电路:

由 U22 (UC3843)、Q27、T6、D45 等元件组成降压反激式变换器,输出+32V,并提供其它低压输出电源; U22 是 PWM 控制器,R167、C124 是定时电阻、电容,第 6 脚输出脉宽信号,R259、R151、R4、C112、R169 组成 400V 过高保护电路,输入第 2 脚; T6、Q27 开关工作,D44、C107、R149 组成 Q27的尖峰脉冲吸收电路; L8、D47、C113 整流滤波,再经 Q26、D46、R154 线性稳压输出 18V 的辅助电源,提供给 U22、U10 及其驱动电路电源; D45、C116、C117、L9、C114、C119 整流滤波输出+32V 电压; R156、R159、R166 输出电压取样,经 U23、U21 光电耦合,回授给 U22 第 1 脚,R171 电流取样经 R168、C121、R157 耦合给 U22 第 3 脚,控制第 6 脚的占空比。

#### 七、+19V、+15V、+12V 低压输出电路:

由 U15 (LM2576)、L5、D36、C90、C91 组成一个降压变换器,产生+19V,提供给 U16 (UC3843)、U26 (UC3843)、U28 (UC3843)、U30 (UC3843) 等电路电源,R118、R65、R120 是输出电压取样,稳定+19V 输出。U17 (LM2576)、L7、D39、C103 组成+15 电路,R131、R139 取样输出稳定 15V; U18 (LM7812)、C105、C106 在+15V 电源的基础上产生+12V; R121、Q22、R125、D37、D38 是+15V、+12V 控制电路,当+5V 产生后,Q22 导通+15V、+12V 才有输出,否则,+5V 无输出,Q22 截止,+15V、+12V 无输出。

#### 八、+5V 电路:

由 U16(UC3843)、Q21、T5、D34等元件组成降压反激式变换器,输出+5V; U16 是 PWM 控制器,R126、C100 是定时电阻电容,R136、C101 组成频率补偿电路,第 8 脚输出基准电压,第 6 脚输出 PWM 控制信号; Q21、T5 开关工作,D35、R117、C89 构成尖峰吸收电路; D34、C92、C93、L6、C96、C97 整流滤波输出+5V 电压; R119、R124、R134 输出电压取样,经 R135 反馈给 U16 第 2 脚,R133、R128、C102 取样电流信号供给 U16 第 3 脚,控制第 6 脚占空比; U19、R130 等元件组成过流保护电路,R130 取样输出电流,当输出电流达到过流点时,R138、R129、R123 分压低于 U19 内部基准电压,U19 断开,U16 第 2 脚电压升高,使 U16 关断输出; U20、Q24、Q25 构成 5V 过压保护电路,当 5V 输出电压升高到保护点时,U20 导通,Q24 导通,R143、R150 分压使 Q25 也导通,U16 的第 8 脚基准电压被拉低,U16 停止工作,5V 无输出;5V 0K 信号电路由 Q23、D42 组成,只有 5V 电压达到 Q23、D42 都导通时,5V 0K 才输出高电平。

#### 九、PFC 电路:

由 U10 (UC3854N)、L3、D13、C50、C51、C52、Q6、Q7、Q8 等元件组成 B00ST 升压电路; U10 是 PFC 集成控制芯片(平均电流型控制模式),其各引脚的功能如下表所示:

| 引脚 | 功能                 | 引脚 | 功能               |  |

|----|--------------------|----|------------------|--|

| 1  | GND 接地端            | 9  | VREF 基准电压端       |  |

| 2  | PKLMT 峰值限制端        | 10 | ENA 起动端          |  |

| 3  | CA OUT 电流放大器       | 11 | Vsense 输出电压检测端   |  |

| 4  | Isense 电流检测器       | 12 | RSET 外接电阻 RSET 端 |  |

| 5  | MultOut 乘法器输出端     | 13 | SS 软驱动端          |  |

| 6  | IAC 输入电流端          | 14 | CT 外接电容 CT 端     |  |

| 7  | VAOUT 电压放大器 VA 输出端 | 15 | VCC 集成电路的供电电压端   |  |

| 8  | Vrms 有效值电源电压端      | 16 | GD 门极驱动端         |  |

第 9 脚是内部基准电压输出+7.5V,第 15 脚接 Vcc,第 1 脚接地,第 12 脚的 R68 和第 14 脚的 C65 决定 IC 内部振荡频率,第 16 脚输出驱动信号,R67、C64 与第 13 脚构成软启动,R59、C60 和 R56、C55、C56 构成频率补偿网络,R61、R54 决定最大工作电流,C54 消除干扰信号对第 2 脚的影响;Q3、Q4、Q5、Q9、Q11、D14、D15、D16、D17、D18、D19、R42、R43、R45、R46、R47、R48、R49、R50 构成三路并联推挽电路,分别驱动Q6、Q7、Q8 三个并联的开关管工作;D13、C50、C51、C52 整流滤波输出385V 左右的电压;R57、R60、C61、R63、R65、C63 构成输入电压取样,R58、R62、R66 构成输入电流检测电路,R53、R52、R55 构成工作电流取样电路,R39、R40、R44、R51 构成输出PFC 电压取样电路,所有上面的取样信号都控制着U10 第 16 脚的输出占空比。

#### 十、Va 电路:

由 U13 (UC3843)、Q13、Q14、D24、D27、T4、D25 等元件构成降压反激式变换器;U13 为 PWM 集成控制芯片,第 7 脚接 19V,第 8 脚基准电源输出,第 5 脚和第 2 脚接地。R88、C85 是定时电阻、电容,第 6 脚脉宽信号输出,经过 R87 限流,控制 Q15、Q16 构成的推挽电路,在 T3 的隔离耦合下驱动Q13、Q14 开关工作,其中 D24、D27 是磁复位二极管;D25、C69、C70、L4、C71、C72 整流滤波输出Va(+75V)电压;R75、R78、R84 取样输出电压输入U2A 的第 2 脚,与第 3 脚基准电压比较,控制 U13 第 1 脚电位,T2 感应开关工作电流经 R108、R92、C81 耦合回 U13 第 3 脚,控制 U13 第 6 脚的输出占空比;U2B等元件构成过流保护,当输出电流达到过流点时,U2B 第 5 脚低于 U2B 第 6 脚基准电压,U2B 第 7 脚控制 U13 第 1 脚为低电位,关断脉冲输出,使 Va 电源停止工作;U14、Q17、Q19 等元件构成过压保护电路,当 Va 输出高于过压保护点时,U14 导通,Q17 也导通,R102、R113 分压使 Q19 导通,从而将 U13 第 8 脚基准电压拉低,控制 U13 关断脉冲输出,使 Va 电源停止工作;U11、Q12、U12 等元件构成 Va 开关控制电路,当 Vason 输入高电平时,U11 导通,Q12 也导通,U12 产生 2.5V 基准电压,从而使 U13 工作产生 Va,否则 Va 无输出;Q20、Q18、D68、D69、D30、D31 构成高压关断放电回路,当 Vason 信号为高电平时,Q12 导通输出高电平时,Q20 导通,Q18 断开,高压电路正常输出;当 Vason 信号为低电平时,Q12 截止输出低电平,Q20 截止,Q18 导通,高压经过 D68、D69、D30、D31 和 R257、R258、R95、R96、R97 向地放电。

#### 十一、 Vs 电路:

U26 (UC3844), Q29, Q30, D57, D55, T9, D54, D58, C130 等元件构成反激式降压变换器, 输出直流电压 180V, U26 (UC3844) 为 PWM 控制芯片,第 7 脚接 19V,第 8 脚基准电源输出,第 5 脚

和第 2 脚接地。第 4 脚外接 R196 和 C141 为定时电阻、电容。第 6 脚为脉宽信号输出,经过 R198 限流,控制 Q31,Q33 构成推挽电路,在 T8 的隔离耦合驱动 Q29,Q30 的导通与截止。其中 D55,D57 为复位二极管。R178,C127 和 R191,C136 构成两路吸收回路;D54,D58,C132,C133,L10,C129 和 C130 构成整流滤波电路,输出 Vs:+180V 电压;R179,R181,R183,R187 取样输出电压输入 U3A 的第 2 脚,与第 3 脚参考电压作比较,控制 U26 的第 1 脚电位。T7 感应开关工作电流经 R205,R210,C146 耦合回 U26 第 3 脚,控制 U26 第 6 脚的输出占空比;U3B 等元件构成过流保护。当输出电流达到过流点时,U3B 第 5 脚电位低于第 6 脚的参考电位,则 U3B 第 7 脚控制 U26 第 1 脚为低电平,关断 6 脚输出;U27,Q32,Q34 等元件构成过压保护电路。当输出电压高于过压保护点时,U27 导通,Q32 也导通,R203,R211 分流使 Q34 也导通,从而将 U26 的 8 脚基准电压拉低,控制器 U26 关断输出信号;U24,Q28,U25 等元件构成 Vs 开关控制电路,当 Vason 为高电平时,U24 导通,Q28 也导通,U25 产生 2.5V 基准电压,从而使 U26 工作,产生 Vs 电压,否则 Vs 无输出。

#### 十二、 Vset-up 电路:

由 U28 (UC3844), Q35, T11, D62 等元件构成反激式升压变换器,输出直流电压 240V; U28 是PWM 控制芯片。R223 和 C159 是定时电阻和定时电容,决定整机工作频率。R234,C161 构成频率补偿电路。第 8 脚基准电压输出。第 6 脚输出脉宽信号,经 R220 限流后控制 Q35 的导通截止; D64,R215,C149 和 R217,C150 构成两路尖峰吸收回路; D62,C152,C153,C154,L11,C155 构成整流滤波电路,输出+240V 电压; R216,R218,R221,R226,R232 输出电压取样电路,经 R233 反馈至 U28 第 2 脚;R230,R225,C160 取样电流信号至 U28 第 3 脚。控制 U28 第 6 脚的占空比;U29,R227等元件构成过流保护电路。R227 取样输出电流,当输出电流达到过流点时,R231,R224,R219 分压低于 U29 内部基准电压,U29 断开,使 U28 第 2 脚电位升高,U28 第 6 脚关断输出。

#### 十三、 Vsc 电路:

本电路和 Vset-up 电路类似。U30 (UC3844), Q36, T12, D65 等元件构成反激式降压变换器,输出直流电压 110V。U30 是 PWM 控制器。R242 和 C173 是定时电阻和定时电容。R253, C175 构成频率补偿电路。第 8 脚基准电压输出。第 6 脚输出脉宽信号,经 R241 限流后控制 Q36 的导通截止。Q36, T12 开关工作。D66, R236, C163 和 R237, C165 构成两路尖峰吸收回路。D65, C167, C168, L12, C169, C170 构成整流滤波电路,输出+110V 电压。R235, R238, R240, R245, R251 输出电压取样电路,经 R248 反馈至 U30 第 2 脚; R250, R246, C174 取样电流信号至 U30 第 3 脚。控制 U30 第 6 脚的占空比。U31, R244 等元件构成过流保护电路。R244 取样输出电流,当输出电流达到过流点时,R239, R247, R254 分压低于 U31 内部基准电压,U31 断开,使 U30 第 2 脚电位升高,U30 第 6 脚关断输出。

电源上输出电压的调节位分别为:

| Vsc    | R245 |

|--------|------|

| Vs     | R183 |

| Vsetup | R226 |

| Va     | R78  |

| V32    | R159 |

| V5     | R124 |

另外, PDP402 和部分 PDP403 产品使用进口电源, 其电压调整位置和输出情况见以下图表, 电源时序相同。

图 2-11

| P801 | 8  | +5Vcntl54, GND54                           |

|------|----|--------------------------------------------|

| P802 | 4  | Vsetup(240~290V), Vsc(60~90V), GND52       |

| P803 | 9  | +5Vdrv, +15Vdrv, Vs(170~190V)52, GND54, NC |

| P804 | 8  | +5Vdrv, +15Vdrv, Vs(170~190V), GND53, NC52 |

| P805 | 6  | Va(60~80V), NC, +15Vdrv, +5Vdrv, GND52     |

| P806 | 6  | Va, NC, +15Vdrv, +5Vdrv, GND52             |

| P807 | 6  | Va, NC, +15Vdrv, +5Vdrv, GND52             |

| P808 | 7  | AC-DET, Relay-ON, +5V ST-BY, GND, Vs ON,   |

|      |    | +5Vcntl-DET, NC                            |

| P809 | 12 | +5V53, +9V52, GND55, NC52                  |

| P810 | 4  | +32Vaudio52, GND52                         |

| P811 | 6  | Va, NC, +15Vdrv, +5Vdrv, GND52             |

#### 第四节 显示屏故障分析

### 1, 开机后待机指示灯亮, 显示器无法转入工作状态:

试用机顶盒或遥控器来打开,如正常,为显示器按键接触不良或按键板故障。如都不行,检查外部交流供电是否在正常范围内。如电源正常,检查电源板与接口板的连接。

#### 2,显示器指示灯表明已经转入工作状态,但显示器无图像:

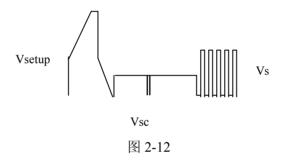

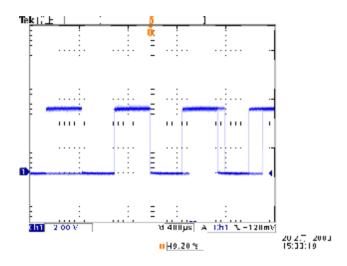

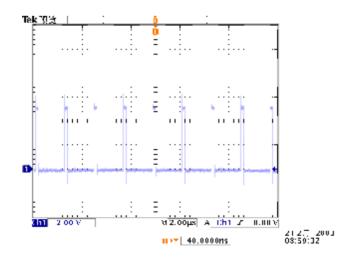

测量主电源板向屏幕的输出电压:如 Vsetup、Vs、Vsc 和 Va 等,看是否正常,如某个电压异常,将相应的连线拔开再开机测量。如仍不正常,则为电源板故障;如电源一切正常,则是相应的驱动电路板故障。另外,如果输出电压在线状态下正常,可以直接测量扫描驱动的输出波形(在绑定 IC 的附近有专门的测量点),如果波形不正常,则为扫描电路的故障。一个子场的参考波形如下图:

#### 3, 局部不显示:

为相对应的地址驱动电路板的故障,有可能是电源插错导致板上器件损坏,也可能是连接问题, 应予以更换或检修。

#### 4, 半屏竖线显示故障:

有一条或两条半场竖线在有图像时常亮,不随外界图像变化。

根据以上对地址驱动电路的分析,应为相应的绑定 IC (COF)输出端的故障,或者是地址电极外部柔性电路的故障。原因有遭到外力作用的损伤而导致断裂或打火烧毁,也存在制造过程中电路的缺陷(短路或断路)。如果是在使用一段时间后出现此类的现象,还有可能是柔性电路与屏幕连接处受热脱开。故在模块的搬运和装配时一定要小心,避免造成此类损坏,对此只能更换显示屏。

图 2-14

#### 5, 半场成组缺色:

常见的缺色以若干条竖线为单位,一般为地址驱动与 Panel 或控制电路的连接故障。可重新连接 以保证接触良好。也可能是地址驱动板上对应的 D 触发器损坏, 检测确认后更换即可。

#### 6, 整场成组缺色:

在双扫描的情况下,考虑到相同位置的地址驱动同时出现故障的可能性较小,基本上应断定为控 制电路的故障, 需更换控制电路板。

#### 7, 竖线闪烁

为局部温度较高(主要是电源上方)所致,有时不止一条甚至连成片,可恢复。应及时关机或降 低环境温度,以免烧毁电路。

图 2-17

#### 8, 横线显示故障:

有单条的横线显示闪烁或不可控,为相应的扫描驱动输出端的故障,多为厂家生产时的缺陷所致。 如果有整个 IC 的损坏,会导致整条的不可控,呈亮或暗的状态。

图 2-18

#### 9, 花屏:

如电源正常启动,无论何种信号均无反应,屏幕为杂乱固定图像,可能为 Vsc 电源输出的故障, 可能为连接接口板和控制板的41针连线松动,需重新连接。如不能解决,则为控制板故障。

#### 10, 局部图像点闪烁:

在某中固定的色彩条件下,局部图像呈雪花状的闪烁。

基本上属于显示屏在制造过程中荧光粉涂布的不均匀超过标准所致, 可适当调低维持电压, 如果 仍不能改善, 只能更换显示屏。

图 2-19

#### 11, 图像底色为黑灰色时满屏噪点干扰

为等离子显示初始化所致,属正常现象,可适当调整亮度和对比度。

#### 12, 图像变暗问题:

由于 PDP 内部具有的保护电路,在显示较大面积高亮度固定画面时,一段时间后将会自动降低 整体亮度,为正常现象。

## 第五节 地址驱动电路检修方法

如果通过更换的方法,确定是地址驱动电路的故障,可以进一步对其进行检测。

通过对中试部生产中出现的损坏地址驱动电路的检修,发现损坏的器件集主要是 FOD19N10(场效应管),ACT541(八位缓冲)和 IR2113S(高低压驱动器),其位号见下表:

|         | 左上            | 左下           | 右上           | 右下           |

|---------|---------------|--------------|--------------|--------------|

| 19N10   | Q101~Q104     | Q105~Q108    | Q1~Q4        | Q5~Q8        |

| ACT541  | ICIC301, IC22 | IC401, IC122 | IC201, IC21  | IC501, IC121 |

| IR2113S | IC302, IC303  | IC402, IC403 | IC202, IC203 | IC502, IC503 |

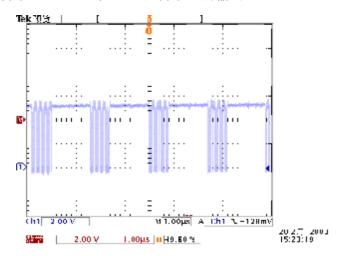

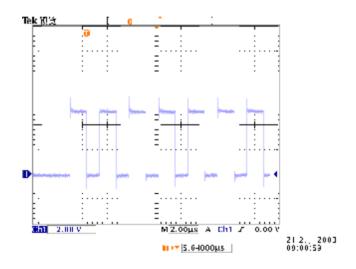

检修时先确定场效应管的好坏,然后正确连接好地址电路上的电源与信号线,拔掉 PDP 电源的三组高压输出线,启动机器到工作状态。测量板上两块 ACT541 的输出信号(板上均有相应的检测点)距离数据接口较近的 541 有 4 个输出检测点,各点的波形如下:

#### 1, PIN11与 PIN12(并联)的输出:

#### 2, PIN13与PIN14(并联)的输出:

3, PIN15 与 PIN16 (并联)、PIN17 与 PIN18 (并联)的输出:

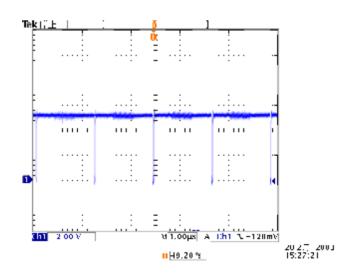

距离数据接口较远的 541 有 2~4 个输出检测点,各点的波形如下:

1, PIN14 的输出:

2, PIN12 的输出:

另外, PIN16 和 PIN18 的输出也为 5V 的方波信号。

541 提供后端 2113S 的输入控制信号,如果检查到上述的波形,则 541 没有问题;否则为 541 的

损坏, 需更换。

在 2113S 输入信号和供电正常的情况下, 其 PIN8 的输出端应当能够分别测量到如下的波形:

如果波形不正确,则为 2113S 损坏。如果波形正确,则可以在与屏的接口和场效应管处测量到类似的信号,表明地址驱动板正常,可以连好电源,开机测试了。

如此可解决绝大部分的问题。

# 第三章 模拟电路部分

#### 一、概述

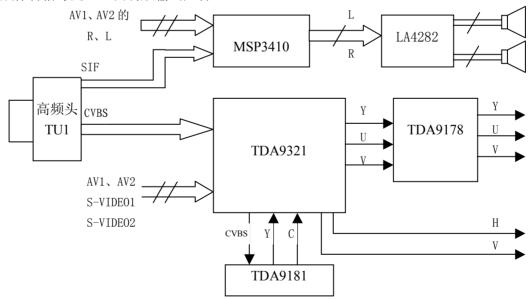

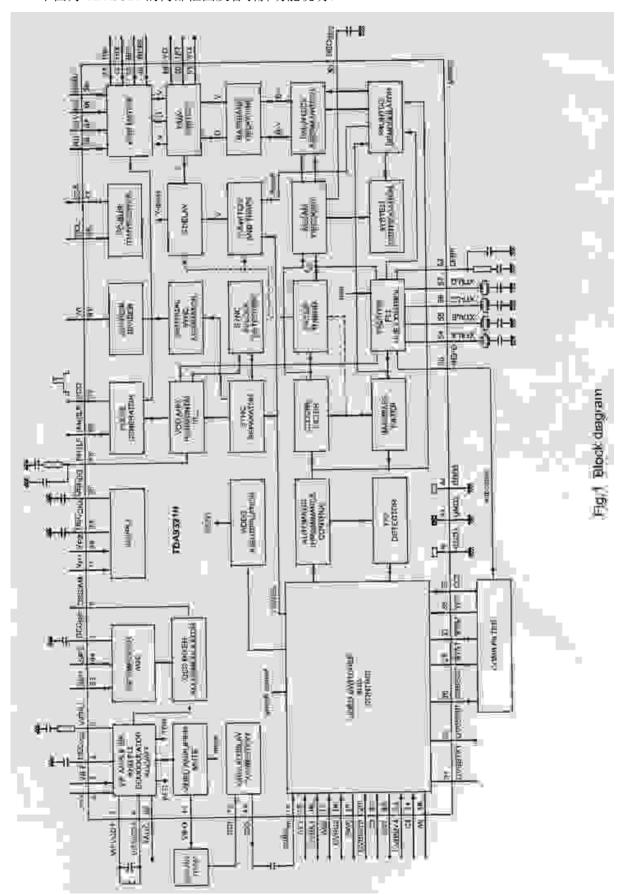

TCL 王牌 PDP403 机顶盒视频解码处理器采用以下数字处理技术:

数字化彩色解码: TDA9321:

数字化梳状滤波器: TDA9181;

数字化图像质量提高: TDA9178;

数字化声音解码处理器: MSP3410G。

#### 二、信号流程图如下:

天线信号进入 TU1 一体化高频头 FQ1216ME, 经高频头内部预中放及中放处理,最后高频头输出为 CVBS 视频信号和第二伴音中频信号 SIF。本高频头为 5V 供电及使用 I²C 总线控制,实现多制式 B/G、DK、I、M 视频解调。由高频头输出的视频信号进入 TDA9321 的第 14 脚,AV1、AV2、的视频信号分别送到 TDA9321 的第 16 脚和第 18 脚。S-VIDEO1、S-VIDEO2 的 Y、C 信号分别送到 TDA9321 的第 20、21 脚和第 23、24 脚。另外 DVD 信号 Y、Cr、Cb 分别送到 TDA9321 的第 37、38、36 脚。各输入信号由内部电子开关选择相应的视频信号送入梳状滤波 TDA9181,经处理后由 TDA9181 的第 14、16 脚分别输出 Y、C 信号,送回到 TDA9321 的第 28、29 脚进行解码处理。解码后由 TDA9321 的第 49、50、51 脚分别输出 Y、U、V 信号。此模拟的 Y、U、V 信号送到 TDA9178 芯片进行画质处理,最后 Y、U、V 信号送到倍行板上进行数字处理。另一方面,由高频头输出的第二伴音信号 SIF 送到 MSP3410 的第 50 脚。AV1、AV2 的 L、R 音频信号分别送到 MSP3410 的第 41、42 脚和第 44、45 脚,经内部电子开关选择相应的音频信号进行音效处理,最后由第 20、21 脚输出给功放,同时 R、L 音频信号由第 25、26 的送到音频输出端子。

总的概括,模拟板完成了视频信号的解码处理,最后以模拟 Y、U、V 信号的形式输出。同时,完成伴音信号处理。由功放输出声音。

#### 三、电路原理介绍。

#### 1. 数字化解码电路。

TDA9321 是总线控制的电视输入处理器。包括中放解调,外部视频、分量、基色输入选择,彩色解码等功能。输出模拟的 Y、U、V 信号和相关的同步控制 H、V 信号,覆盖全部的视频制式。结合本机型的应用,高频头已完成中放解调,输出 CVBS 视频信号。所以 TDA9321 就不要使用中放解调部分电路。与中放解调相关的引脚除接地端外都悬空不接。另外,在视频制式方面考虑,只接 3.58M

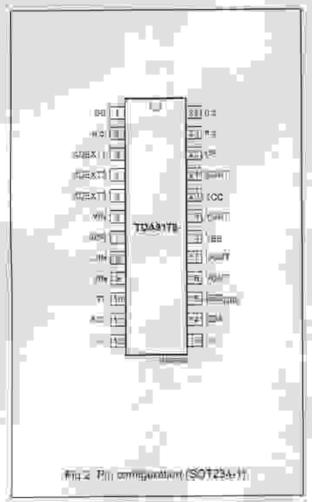

和 4.43M 晶体,完成 PAL、BG、DK、I 和 NTSC-M 等视频制式。 下面为 TDA9321 的内部框图及各引脚功能说明。

# 12C-bus controlled TV input processor

TDA9321H

#### PINHING

| SYMBOL         | PIN   | DESCRIPTION                                        |

|----------------|-------|----------------------------------------------------|

| DES            | 1)    | SHF AGC Monutiling                                 |

| WEI            | Π.    | VF (nout )                                         |

| VIFZ           | 3     | vif Impul 2                                        |

| DESCUE         | #     | VIF-WGC decoupling                                 |

| QSS/AW         | ü     | CONTRACTOR OF THE AM HAME BUILDER                  |

| VITTLE         | 6     | VIE TILL DIGG                                      |

| VIEVEDY        | 7     | VIE VICO NUMBI ENTRI I                             |

| VE ACCIS       | ô     | VIII VOO turmii orrailli a                         |

| GND1           | ۵     | minik ittpply amund                                |

| VIECE/         | - Out | VIF gatignal                                       |

| Ven            | 01    | pastice enough 1 0 fill VII                        |

| GIM            | 3後    | group stalley concentral litters                   |

| GDB)           | t3    | dum geles actuallouters                            |

| CVESHI         | 1/1   | internal CVSS input                                |

| <u>A</u> VI    | 15    | W/Intritit                                         |

| CVB84          | 16    | dyas mau 1                                         |

| AV:            | 120   | AV Impural                                         |

| CVB5.          | 18    | <b>《</b> 外报告 班班··································· |

| SWII           | 18    | SWITCH OUTSHIED IN THE CHINE                       |

| CVESIYS        | 20    | CVBS or harmonical Impart 3                        |

| C3             | 121   |                                                    |

| 3144           | 22    | WIND COURT OF BUILDING SPIRIT                      |

| CVB8/Y4        | 23    | ASYRS OF HITTHWARE HIGHER                          |

| ψ <sub>1</sub> | 24    | rimaniano hautil                                   |

| 8781           | 26    | BVSBM OUTDUT 1 TO LUTTE THE                        |

| <b>AVBECF</b>  | 28    | LISUS cumul for comb Illies:                       |

| 8752           | 21    | KABIBILI ONULLUI TIMO CONTINUIDE                   |

| YCF            | 20    | Jumiation I mail from court file:                  |

| (Safe          | 49    | ாருள்ள காக் விடிக்கார்கள் காக் விடிக்க             |

| PAERO:         | 30    | interpolation (1871) political (1881)              |

| GNUZ           | 31    | umal sounty grand                                  |

| CURSEU)        | 32    | CVES suitbut list [Actors-in-History)              |

| SYMBOL             | PIN        | DESCRIPTION                                             |  |

|--------------------|------------|---------------------------------------------------------|--|

| DEC≤m              | 73         | андия выпрлу фесонали                                   |  |

| CVESTXT            | 52         | CVRS cutput to releiant                                 |  |

| DEC <sub>ika</sub> | 35         | реса двр авсоции                                        |  |

| 811                | 篗          | ited inguite                                            |  |

| GII                | 37.        | green mput 1                                            |  |

| 811                | 3,8        | bkie inpili I                                           |  |

| Rud1               | 35         | RG6 meartant imput                                      |  |

| prepo:             | 40         | RGS laseitini imput ill                                 |  |

| RYE                | 41         | TECHTON Z                                               |  |

| GIE.               | 112        | grami input 2:                                          |  |

| BIE                | A.         | him=mark≥                                               |  |

| PPN[55             | 411        | promod 3:                                               |  |

| Via                | 4ã         | рение априу 2 = 8 V/                                    |  |

| SIL                | #8         | EBMBI DIODX:(DOL) (PC httl)                             |  |

| SD4                | HÎ.        | Sand data ingal/Antini (1955 birs)                      |  |

| :AB                | 48         | вашезз выест паш (Г.С. тив)                             |  |

| 100                | 19         | штиний жүші.                                            |  |

| DO                 | 50         | Li-signer output:                                       |  |

| 1/2                | 31         | Vişilgiyal etilleril                                    |  |

| LEBR.              | 52         | loop fines our at 1 male describs                       |  |

| DECSEL             | 53         | SECVIN BIT ABBURDING                                    |  |

| XTALE              | :54        | SPYSSELLY AUSD IN MICE                                  |  |

| KTALE              | <u>6</u> 4 | c/yelsil E/IS:882058 MH3T                               |  |

| KIALC              | 56         | rayees Cutattae 1 Militin                               |  |

| STAILE)            | .57P       | ¤ystel Ø (3.579545 MH≥)                                 |  |

| 77112.5            | 56         | Emains 1 moduling                                       |  |

| 900                | 30         | sandrasile pilas outor                                  |  |

| HACIF.             | 100        | manazinini puwa langun ar dilami pintau<br>mpyakaninini |  |

| VA:                | 164        | VERTICES DUSSE OUTDUIT                                  |  |

| Walge.             | 67.        | IIII AGC output                                         |  |

| SHI                | 1163       | SIE maai II                                             |  |

| 5872               | 64         | SIF im12                                                |  |

# 2. 数字化梳状滤波器电路。

构成图像的亮度和色度信号在视频信号中是混在一起的。在组成这一方案时采用了频谱间置技术,使得从理论上他们可以被无失真分离。早期的电视因简单地使用频率分割法,色度信号和亮度信号频域重叠的部分相互造成影响。表现为彩色区域界限的地方出现黑白点和细的白线条上会看到蠕动的彩纹。梳状滤波器是保证图像细节的情况下解决视频信号亮色互窜的唯一方法。TDA9181 兼容 PAL、BG、DK、I 和 NTSC-M 等制式,从 TDA9321 输出的 CVBS 或 Y 信号送到 TDA9181 的第 12 脚和第 3 脚,在外部控制信号作用下,完成 Y/C 分离。

下面是 TDA9181 的内部框图及各引脚功能说明。

# Integrated multistandard comb filter

TDA9181

# Integrated mullistandard comb lilter

# TDA9181

# PINHING

| SYMBOL            | PIN  | DESCRIPTION                                        |  |  |

|-------------------|------|----------------------------------------------------|--|--|

| O <sub>III</sub>  |      | Imomilianes signal listivi                         |  |  |

| VIPSEL .          |      | liciti wiich saled intiil                          |  |  |

| VIEVES            |      | Linder College Service Community Service           |  |  |

| 0ANO              |      | digitim gracury!                                   |  |  |

|                   | 1    | CONTRACTOR AND |  |  |

| V <sub>resp</sub> | q    | BURGI MADON ASHILL                                 |  |  |

| V <sub>OIM</sub>  |      | HQW BHDIS STREET                                   |  |  |

|                   |      | SENIOU SUBCEMIII BEIOCI JODGE.                     |  |  |

| TBC               | 4    | ALLIAN ALIbertreial Moch Signal                    |  |  |

| 8Y.82             | 10   | نابيرة كالسائدة عاميدية                            |  |  |

| ån&I              |      | some the Limited                                   |  |  |

| VIAVESII          | 13   | formeror of Cytel Ingrad filling                   |  |  |

| A⊴∆fti            | 13   | luissoil Bearrai (mfius terminous                  |  |  |

| W. VELSON         | 13   | јутиненов от Субе акуше опициј                     |  |  |

| \$\(\tau_{1}\)    | I.K  | Ikilbul imiteksississi lotutt                      |  |  |

| Valid             | ( lå | (imminimental Elektro) bistool                     |  |  |

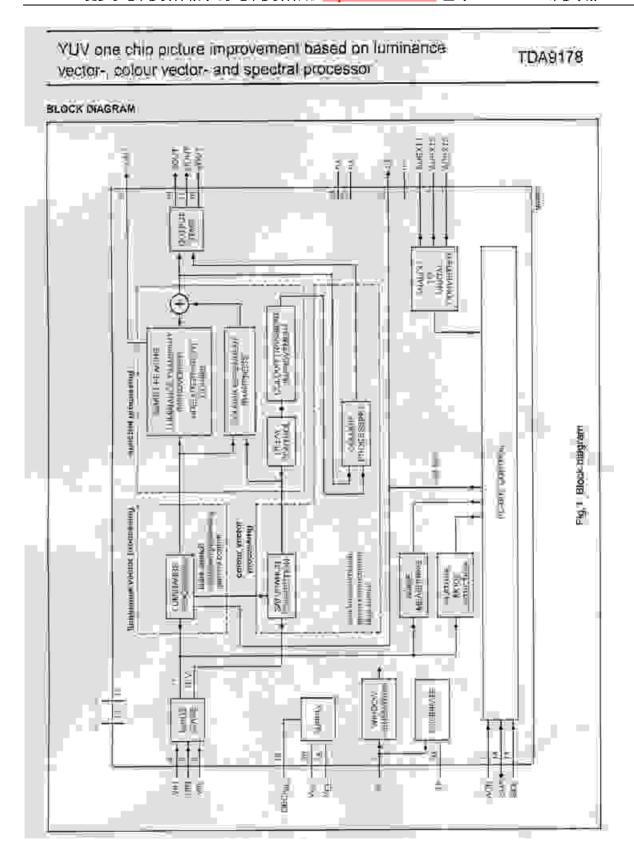

#### 3. 数字化画质改善电路。

在 TDA9178 集成内部完成以下几种图像质量改善措施: 峰化 (peaking): 夸张高频信号,使图像细节更清晰; 核化降噪(coring): 在保持不损失轮廓的情况下衰减小幅度的高频信号(一般都是噪声), 使画面更干净。

亮度瞬态改善(LTI): 使画面黑白过渡鲜明, 晶莹剔透。

色度瞬态改善(CTI): 使画面彩色过渡鲜明,尤使人物皮肤在背景下特别突出。

伽玛校正 (GAMMA CORRECTION):校正屏的亮度非线性问题,改善亮区层次感。

黑电平伸展 (BLACK STRETCH): 能增强暗区层次。

蓝电平伸展 (BLUE STRETCH): 能增强天空和海水等景物的蓝色电平,让画面更鲜艳夺目。

由 TDA9321 输出的 Y、U、V 信号直接送到 TDA9178 的 Y、U、V 输入端,在外部控制信号的作用下,经过各种处理后,直接输出 Y、U、V 信号。考虑到后接倍行板输入信号的要求,输出的 Y、U、V 经过射随及分压电路,最终保证 Y、U、V 的信号幅度在 0.7Vp-p 左右。

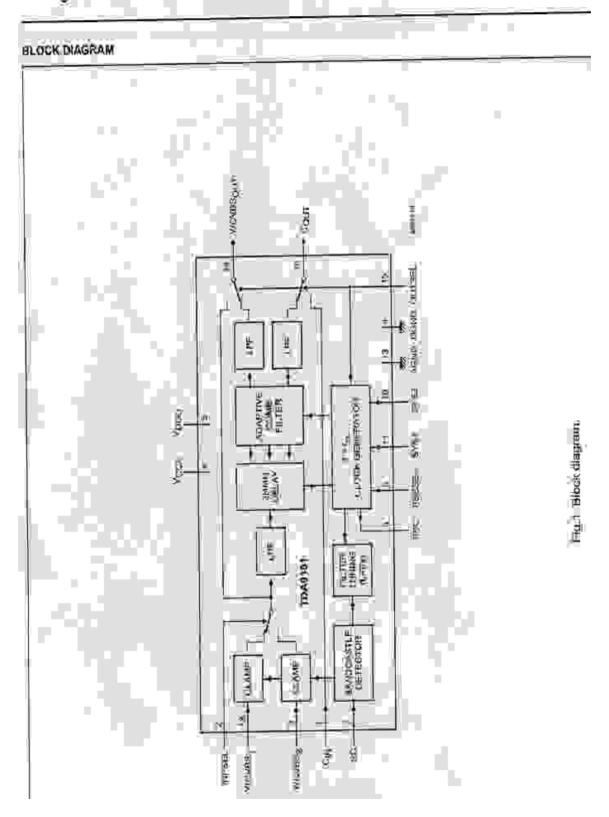

#### 4. 数字化声音解码处理器

数字化的声音解码电路以经过准分离电路得到的第二伴音中频信号 SIF 为输入,数字化后进行解码。MSP3410 可以解调几乎所有制式的普通伴音、立体声与双语、以及丽音信号。在芯片内部通过编程来对不同的伴音系统来处理,因而具有较大的灵活性。解调得到的声音信号或者是从其它途径输入的声音信号可以在芯片中得到所有的处理,例如高低音、等响度控制、环绕声、自动音量控制等。下面为声音信号的流程框图:

从以上流程图可知道,各种声音输入信号经 MSP3410 解调后,由左右声道输出到功放电路进行放大。同时,AV 输出信号送到音频输出端子,完成声音通道的处理。

注: 此芯片在其它资料中作过介绍,本处从简。

# YUV one chip picture improvement based on furninance vector, colour vector, and spectral processor

**3719AUT**

#### PINNING

| SYMBOL  | RIN  | DESCRIPTION                 |

|---------|------|-----------------------------|

| S0      | 1    | ■nd==ttili inpul            |

| n x     | 2    | rial commented:             |

| ACEXT1  | 78   | ACCURPANT                   |

| ACEXT2  |      | MESC liquit 2               |

| ACRESTR | 3    | /ASSC HODGE S               |

| YH4     | A.   | Aurinarius Argul            |

| ADFI    | 9    | ENDOTASE BEIOCION INDICI    |

| UIN     | 4    | U signal (figur             |

| VtN     | 30   | /V eignal Inoul             |

| TH      | 11/  | Test bulk                   |

| SCI_    | 11.5 | MILL North Hilling (FC-FFE) |

| rt:t:   | 12   | рог солинстей               |

| SYMBOL | PM  | DESCRIPTION                      |  |

|--------|-----|----------------------------------|--|

| n//    | 13  | hat connected                    |  |

| SDA:   | 14  | serral date impullinapu (120-bas |  |

| DECOME | 48  | weshing differ short             |  |

| vout   | 18  | N siggell output                 |  |

| DOM:   | 17  | U airmitio quet                  |  |

| Vire   | IΒ  | FERMING                          |  |

| YOUT   | 19  | amanana cultur                   |  |

| V      | 30  | #typetvi//elthéré                |  |

| डेक्का | -21 | SCAVEM output                    |  |

| DF-    | 22  | min flesh dutpul.                |  |

| ńli:   | 23  | ndtesmeded                       |  |

| m-=    | 24  | пол Энтины                       |  |

第30页

# 第四章 逐行处理电路

#### 一、概述

我国现行的电视标准是 50Hz 隔行扫描,即每帧画面为 625 行,每帧画面分两场扫描,产生奇数场和偶数场,每场 312.5 行,每秒钟传送 25 帧画面,即 50 场信号。接收端将得到的奇数场和偶数场信号均匀镶嵌,即可构成一幅幅完整的图象。这种方法可有效地简化电视系统,减小视频带宽,具有较大的经济价值。

但是,这种系统也有明显的缺陷:

- 1. 由于采用隔行扫描,使每一行出现的频率比逐行扫描低了一倍,因此会不可避免的出现行间 闪烁和行间抖动,对图象的清晰度影响较大。

- 2. 由于采用了隔行扫描,每场的扫描线只有逐行扫描的一半,使得行间距加大,就产生了行结构线,画面显得粗糙、不细腻,屏幕越大越明显。

- 3. 因为每秒传送 50 场信号,接近人眼的临界频率 46HZ,会产生大面积闪烁。

这些问题不但会影响画质,而且会影响视力,因此近几年来人们一直在努力改善,随着数字化技术的发展,先后出现了100Hz 隔行扫描、1250 线精密显像、75Hz 隔行扫描及60Hz 逐行扫描等技术。100Hz 隔行扫描技术将场扫描频率加倍,消除了大面积闪烁,但仍有行间闪烁和行结构线;1250 线精密显像技术将每场行扫描线加倍,提高了扫描线密度,但还不能解决大面积闪烁问题;75Hz 隔行扫描技术是将场扫描频率提高为原来的1.5倍,解决了大面积闪烁问题,但和100Hz 技术一样,仍有行间闪烁和行结构线;而60HZ 逐行扫描技术将每场的行扫描线加倍,同时将场扫描频率提升为60Hz,远离人眼的临界频率,使画面细腻、清晰,又不闪烁,是目前比较理想的一种解决方案。

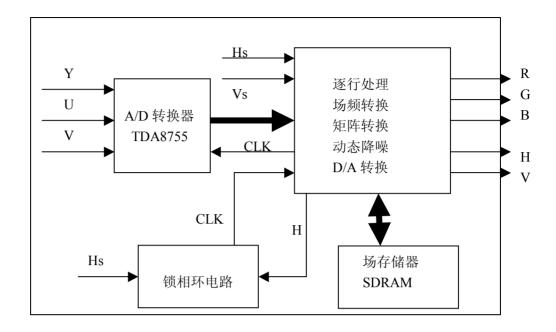

本机倍行处理板采用的就是 60HZ 逐行扫描电路,其主要功能是将模拟板送入的 50HZ 隔行 YUV 信号进行数字化处理,及矩阵变换得到 60Hz 逐行扫描的 RGB 信号,使画面细腻、不闪烁。

60Hz 逐行扫描电路采用了自适应运动检测和补偿的逐行处理方式,对图像进行 4 个场的存贮,其中两个奇场和两个偶场。然后对存贮的奇场和偶场信号交叉运算,得出一个奇场和一个偶场信号。将新产生的每一场信号的行扫描信号分别插入到当前信号的对应行,使画面的行扫描线加倍,实现逐行信号处理。采用这种处理方式不但增加了扫描线,而目增加了图像相关信息,使图像的连续性得到增强,减少运动画面产生的锯齿,使图像更细腻、自然,提高了图像质量。

另外,还采用 5 场重复 1 场的方法,将场频从 50Hz 提升到 60 Hz,远离人眼的闪烁临界频率(人眼闪烁感的临界频率是 46Hz),消除了 50Hz 产生的大面积闪烁,使图像更加稳定。

逐行处理电路模块框图如下:

#### 二、信号流程

50Hz 的 Y. U. V 模拟信号经滤波、耦合电路从数-摸转换器(ADC)TDA8755 (U1)的(3)、(7)、(9)脚输入,经 A/D 变换后,8bit 亮度数字信号从(24)~(31)脚输出,加到 NV320 (U6)的(171)~(176)和(178)、(179)脚。4bit 的色差数字信号从(19)~(22)脚输出,加到 NV320 的(193)~(196)脚,TDA8755 输出的图像数据为 Y: U: V=4:1:1 格式。A/D 变换所需的时钟信号、行同步信号、箝位脉冲均由 NV320 电路内部产生,分别从 U1 的(17)、(16)、(15)脚输入。

MC74HCT4046A(U3和U4)是两个锁相环集成电路,内部由压控振荡器和相位比较器组成。U3(4)脚输出的压控振荡信号(LLCF)送到NV320的(202)脚,作为读出倍频扫描数字信号的工作时钟信号。为了使U3和U6的工作同步,U6(203)脚输出的行频信号(HRCF)再送回U3的(3)脚,和(14)脚输入的模拟行同步脉冲鉴相,鉴相误差信号从(13)脚输出经R4加到(9)脚,控制U3压控振荡器的频率。(9)脚外接的C27、R7是滤波元件。

U4(4)脚输出的压控振荡信号(LLDA2)送到扫描变换处理集成电路 NV320 的(24)脚,作为该电路工作模式切换的时钟信号。U6(168)脚输出的行频信号(HRAF)也送回 U4 的(3)脚,和(14)脚输入的模拟行同步脉冲鉴相,鉴相误差信号从(13)脚输出经 R10 加到(9)脚,控制 U4 压控振荡器的频率。

NV320 是逐行扫描变换处理电路,IS42G32256 是帧存贮器。数字化的 50Hz 图像信号,在这两块 IC 内完成 50Hz→60Hz、隔行→逐行的扫描变换。为了提高处理速度,NV320 和 IS42G32256 之间的数字信号传递采用并行方式,其中亮度数字信号(DQ0~DQ31)用 32 个引脚互连,色差数字信号(A0~A10)用 11 个引脚互连。NV320 和 IS42G32256 是倍频扫描处理组件的核心电路,可适应隔行、逐行、逐行加运动补偿三种插补模式。

从连接端子 P4 输入的 IIC 总线 (SCL)、(SDA) 信号,分别加到 (U6) 的 (35)、(34) 脚,作为模式控制电路与微处理器之间的程序通讯信号。P5 的 IIC 总线 (SCL)、(SDA) 信号及中断控制信号用于机顶盒与显示屏之间的通讯控制,包括开关机、遥控、按键操作等。

经过上述变换处理后,再经过矩阵转换,将 YUV 信号转成 RGB 信号,然后在 NV320 内部完成 D/A 变换,分别从(69)、(56)、(63) 脚输出 60Hz 逐行扫描的模拟 RGB 信号,再经 Q2~Q4 和偏置电路组成的三个缓冲级输出,连到数字处理板。倍频扫描的行(HS)、场(VS) 同步信号经 74HC125(U5) 驱

动输出。

# 三、各 IC 引脚功能表

# 1. TDA8755 引脚功能表

| 符号   | 脚号 | 功能          | 符号   | 脚号 | 功能        |

|------|----|-------------|------|----|-----------|

| NC   | 1  | 空脚          | CLK  | 17 | 时钟输入      |

| REG1 | 2  | 内部电路去耦接点    | DGND | 18 | 数字地       |

| INY  | 3  | Y模拟输入       | D'0  | 19 | V数据输出     |

| REG2 | 4  | 内部电路去耦接点    | D'1  | 20 | V 数据输出    |

| CLPY | 5  | Y箝位电容接点     | D'2  | 21 | U数据输出     |

| VccA | 6  | +5V 电源(模拟)  | D'3  | 22 | U数据输出     |

| INU  | 7  | U模拟输入       | Vcc0 | 23 | 输出级+5V 电源 |

| SDN  | 8  | 稳压滤波和模拟参考电压 | D0   | 24 | Y数据输出     |

| INV  | 9  | V 模拟输入      | D1   | 25 | Y数据输出     |

| AGND | 10 | 模拟地         | D2   | 26 | Y数据输出     |

| CLPU | 11 | U 箝位电容接点    | D3   | 27 | Y数据输出     |

| CLPV | 12 | V 箝位电容接点    | D4   | 28 | Y数据输出     |

| REG3 | 13 | 内部电路去耦接点    | D5   | 29 | Y数据输出     |

| CE   | 14 | 片选骑入        | D6   | 30 | Y数据输出     |

| CLP  | 15 | 箝位控制输入      | D7   | 31 | Y数据输出     |

| HREF | 16 | 行基准信号       | VccD | 32 | +5V 数字电源  |

# 2. 74HCT4046A 引脚功能表

| 2. I mor to for Jim 25 feet |    |            |         |    |            |  |

|-----------------------------|----|------------|---------|----|------------|--|

| 符号                          | 脚号 | 功能         | 符号      | 脚号 | 功能         |  |

| PCP OUT                     | 1  | 相位比较器脉冲输出  | VCO IN  | 9  | VCO 输入     |  |

| PC1 OUT                     | 2  | 相位比较器 1 输出 | DEM OUT | 10 | 解调器输出      |  |

| COMP                        | 3  | 比较器输入      | R1      | 11 | 电阻 R1 接点   |  |

| IN                          |    |            |         |    |            |  |

| VCO OUT                     | 4  | VCO 输出     | R2      | 12 | 电阻 R2 接点   |  |

| INH                         | 5  | 输入抑制       | PC2 OUT | 13 | 相位比较器 2 输出 |  |

| C1A                         | 6  | 电容 C1 接点 A | SIG IN  | 14 | 信号输入       |  |

| C1B                         | 7  | 电容 C1 接点 B | PC3 OUT | 15 | 相位比较器3输出   |  |

| GND                         | 8  | 地          | Vcc     | 16 | 电源         |  |

# 3. NV320 引脚功能表

| 符号              | 脚号           | 功能          | 符号          | 脚号             | 功能               |

|-----------------|--------------|-------------|-------------|----------------|------------------|

| DQ6, DQ5        | 1,2,         | 倍频Y数字信号     | P1VDD       | 102            | 3.3V 电源          |

| PVDD            | 3            | 3. 3V 数字电源  | PVDD        | 104            | 3. 3V 数字电源       |

| DQ4~DQ2         | <b>4</b> ∼6, | 倍频 Y 数字信号   | PVSS        | 107, 108       | 数字地              |

| PVSS            | 7            | 数字地         | P60         | 110            | 50/60Hz 切换接 3.3V |

| DQ1, DQ0, DQ15  | 8~10         | 倍频 Y 数字信号   | OFQ         | 111            | 数字地              |

| PVDD            | 11           | 3. 3V 数字电源  | PVDD, PLLFS | 112, 113       | 3. 3V 数字电源       |

| DQ14~DQ12       | 12~14,       | 倍频 Y 数字信号   | PVSS        | 114~119        | 数字地              |

| PVSS            | 15           | 数字地         | A3          | 120            | 倍频 U. V 数字信号     |

| DQ11 $\sim$ DQ9 | 16~18        | 倍频 Y 数字信号   | PVDD        | 121            | 3. 3V 数字电源       |

| PVDD            | 19           | 3. 3V 数字电源  | A2∼A0, A8   | $122 \sim 125$ | 倍频 U. V 数字信号     |

| DQ8             | 20           | 倍频 Y 数字信号   | PASS        | 126            | 数字地              |

| DQMO            | 21           | Y数字模式       | A10         | 127            | 倍频 U. V 数字信号     |

| CLK             | 22           | 时钟          | CS          | 128            | 片选               |

| PVSS            | 23           | 数字地         | RAS         | 129            | 读选择              |

| LLDA2           | 24           | 工作模式切换时钟    | PADD        | 130, 131       | 3. 3V 数字电源       |

| PVSS            | 25           | 数字地         | XTALO       | 132            | 晶振               |

| A9              | 26,          | 倍频 U.V 数字信号 | XTALI       | 133            | 晶振               |

| PVDD    | 28     | 3.3V 数字电源    | PVSS      | 134            | 数字地         |

|---------|--------|--------------|-----------|----------------|-------------|

| A7, A6  | 29, 30 | 倍频 U. V 数字信号 | CAS       | 135            | 片地址选择       |

| PVDD    | 31     | 3. 3V 数字电源   | WE        | 136            | 写允许         |

| A5, A4  | 32,33  | 倍频 U. V 数字信号 | DQM1      | 137            | 数字模式        |

| SDA     | 34     | IIC 数据       | DQ23      | 138            | 倍频 Y 数字信号   |

| SCL     | 35     | IIC 时钟       | PVSS      | 139            | 数字地         |

| PVSS    | 36     | 数字地          | DQ22~DQ19 | 140 ~          | 倍频Y数字信号     |

|         |        |              |           | 143,           |             |

| PCLK    | 37     | 扫描变换时钟       | PVDD      | 144            | 3. 3V 数字电源  |

| HSQ     | 38     | 倍频行同步        | DQ18~DQ16 | 145 ~          | 倍频 Y 数字信号   |

|         |        |              |           | 147,           |             |

| PVDD    | 40     | 3. 3V 数字电源   | PVSS      | 148            | 数字地         |

| VSQ     | 41     | 倍频场同步        | DQ31~DQ28 | 149~152        | 倍频Y数字信号     |

| RADJ    | 43     | 电源参考电阻       | PVDD      | 153            | 3.3V 数字电源   |

| PVSS    | 44     | 数字地          | DQ27~DQ25 | 154~156        | 倍频Y数字信号     |

| PVDD    | 48     | 3. 3V 数字电源   | PVSS      | 157            | 数字地         |

| ADGND   | 50     | 数字地          | DQ24      | 158            | 倍频Y数字信号     |

| ADVDD   | 51     | 3.3V 数字电源    | P3VDD     | 160            | 3.3V 电源     |

| PVSS    | 53     | 数字地          | P3GND     | 161            | 数字地         |

| YA      | 56     | 倍频 Y 模拟输出    | PVDD      | 162            | 3. 3V 数字电源  |

| YVDD    | 57     | 3. 3V 模拟电源   | PVSS      | 166            | 数字地         |

| YGND    | 58     | 模拟地          | CLP0      | 167            | 箝位信号输出      |

| PVDD    | 61     | 3. 3V 数字电源   | HREFO     | 168            | 行参考信号输出     |

| UA      | 63     | 倍频 U 模拟输出    | CLKO      | 169            | 写入时钟        |

| UVDD    | 64     | 3. 3V 模拟电源   | PVDD      | 170            | 3.3V 数字电源   |

| UGND    | 65     | 模拟地          | Y0∼Y5     | $171 \sim 176$ | Y数字信号输入     |

| COMP    | 68     | 补偿电容接点       | PVSS      | 177            | 数字地         |

| VA      | 69     | 倍频 V 模拟输出    | Y6, Y7    | 178, 179       | Y数字信号输入     |

| VVDD    | 70     | 3.3V 模拟电源    | PVDD      | 182            | 3.3V 数字电源   |

| VGND    | 71     | 模拟地          | V0∼V3     | $189 \sim 192$ | 低4位V入口接地    |

| VREFOUT | 74     | 参考电压输出       | V4∼V7     | 193~196        | U. V 数字信号输入 |

| AGND    | 75     | 模拟地          | VS        | 198            | 场同步输入       |

| VREFIN  | 76     | 参考电压输入       | HS        | 199            | 行同步输入       |

| AVDD    | 77     | 3. 3V 数字电源   | LLC       | 202            | 读出时钟        |

| PVSS    | 78, 79 | 数字地          | RESET     | 204            | 复位          |

| PVDD    | 83, 85 | 3. 3V 数字电源   | P2GND     | 205            | 数字地         |

| PVSS    | 89     | 数字地          | P2VDD     | 206            | 3. 3V 数字电源  |

| PVDD    | 93     | 3. 3V 数字电源   | PVSS      | 207            | 数字地         |

| PVSS    | 98     | 数字地          | DQ7       | 208            | 倍频 Y 数字信号   |

| P1GND   | 101    | 数字地          |           |                |             |

# 4. IS42G32256 引脚功能如表:

| 符号         | 脚号     | 功能        | 符号         | 脚号     | 功能         |

|------------|--------|-----------|------------|--------|------------|

| DQ27       | 1,     | 倍频 Y 数字信号 | DSF        | 53     | 数字地        |

| VccQ       | 2      | 3.3V 数字电源 | CKE        | 54     | 3. 3V 数字电源 |

| DQ28, DQ29 | 3,4    | 倍频 Y 数字信号 | CLK        | 55     | 时钟         |

| GNDQ       | 5      | 数字地       | DQM3, DQM1 | 56, 57 | 数字转换模式     |

| DQ30, DQ31 | 6,7    | 倍频 Y 数字信号 | VCCQ       | 59     | 3. 3V 数字电源 |

| VccQ       | 8      | 3.3V 数字电源 | DQ8, DQ9   | 60, 61 | 倍频 Y 数字信号  |

| DQ16, DQ17 | 9,10   | 倍频 Y 数字信号 | GNDQ       | 62     | 数字地        |

| PVSS       | 11     | 数字地       | DQ10, DQ11 | 63, 64 | 倍频 Y 数字信号  |

| DQ18~DQ19  | 12,13  | 倍频 Y 数字信号 | VCC        | 65     | 3. 3V 数字电源 |

| PVDD       | 14, 15 | 3.3V 数字电源 | GND        | 66     | 数字地        |

| GND        | 16     | 数字地       | VCCQ       | 67     | 3. 3V 数字电源 |

| DQ20, DQ21 | 17, 18       | 倍频 Y 数字信号   | DQ12, DQ13 | 68, 69 | 倍频 Y 数字信号  |

|------------|--------------|-------------|------------|--------|------------|

| GNDQ       | 19           | 数字地         | GNDQ       | 70     | 数字地        |

| DQ22, DQ23 | 20, 21       | 倍频 Y 数字信号   | DQ14, DQ15 | 71, 72 | 倍频 Y 数字信号  |

| VCCQ       | 22           | 3. 3V 数字电源  | VCCQ       | 73     | 3. 3V 数字电源 |

| DQMO, DQM2 | 23, 24       | 数字地         | DQ0, DQ1   | 74, 75 | 倍频 Y 数字信号  |

| WE         | 25,          | 写允许         | GNDQ       | 76     | 数字地        |

| CAS        | 26           | 片选          | DQ2, DQ3   | 77, 78 | 倍频 Y 数字信号  |

| RAS        | 27           | 读选择         | VCCQ       | 79     | 3.3V 数字电源  |

| CS         | 28           | 片选          | DQ4, DQ5   | 80, 81 | 倍频 Y 数字信号  |

| A10, A8    | 29,30        | 倍频 U.V 数字信号 | GNDQ       | 82     | 数字地        |

| A0∼A3      | $31 \sim 34$ | 倍频 U.V 数字信号 | DQ6, DQ7   | 83,84  | 倍频 Y 数字信号  |

| VCC        | 35           | 3.3V 数字电源   | GNDQ       | 85     | 数字地        |

| PVSS       | 36, 46       | 数字地         | VCC        | 96     | 3.3V 数字电源  |

| A4~A7, A9  | $47 \sim 51$ | 倍频 U.V 数字信号 | DQ24, DQ25 | 97, 98 | 倍频 Y 数字信号  |

|            |              |             | GNDQ       | 99     | 数字地        |

|            |              |             | DQ26       | 100    | 倍频 Y 数字信号  |

| GND        | 37           | 数字地         | PCLK       | 92     | 扫描变换时钟     |

| VCC        | 38           | 3.3V 数字电源   | SCL        | 93     | IIC 时钟     |

| nSTATUS    | 39           |             | SDA        | 94     | IIC 数据     |

| SDAF       | 40           | IIC 数据      | LLC        | 97     | 显示时钟       |

|            |              |             | RESET      | 100    | 复位         |

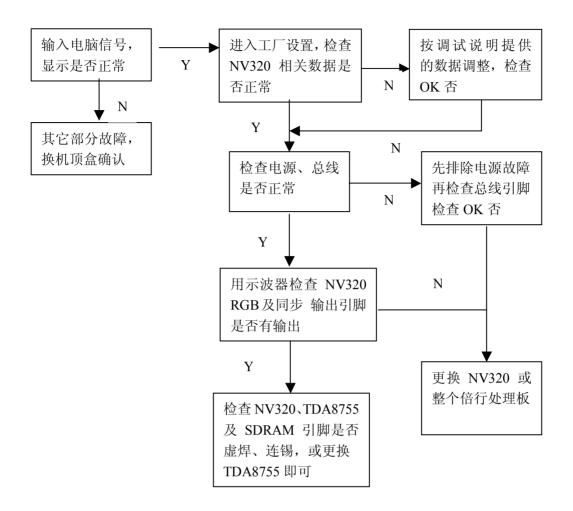

# 四、倍行板检修流程

倍行板(60Hz逐行处理电路)出现故障后,可能会导致以下现象:

- 1. 画面显示蓝屏,无TCL标志(LOGO)。

- 2. 画面显示错乱,不同步。

- 3. 画面垂直方向显示不全,只有一部分甚至全部为灰屏显示。

- 4. 画面颜色大部分正确,但局部有彩斑状干扰,如人脸、皮肤等。

出现以上故障或其它现象,可按以下流程修检:

# 第五章 数字处理电路

# 一,数字板的图象信号选择电路

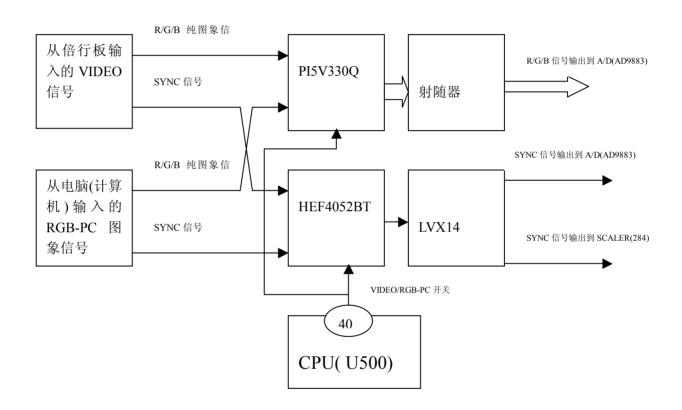

数字板的 VIDEO (TV, AV1, AV2, S\_VIDEO1, S\_VIDEO2, YUV) / RGB-PC 图象信号切换电路的目的是把从倍行板输入的 VIDEO (TV, AV1, AV2, S\_VIDEO1, S\_VIDEO2, YUV) 图象信号,以及从电脑(计算机)输入的 RGB-PC 图象信号,通过一系列开关选择电路,传输到数字板的图象数字化电路。数字板的 VIDEO (TV, AV1, AV2, S\_VIDEO1, S\_VIDEO2, YUV) / RGB-PC 图象信号切换电路方框图如图所示,由一组图象切换开关 (PI5V330Q 和射随)及一组同步切换开关 (HEF4052BT 和 LVX14)组成。

#### R/G/B 纯图像信号的选择

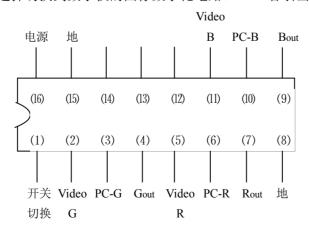

R/G/B 纯图像信号的选择电路如图所示,其主要任务把由前级(倍行板及 PC)输出的纯图像信号通过选择电路,选择切换到数字板的图像数字化电路。U603 各引出脚的功能见表。

| 序号       | 符号      | 输入/输出 | 功能说明            |

|----------|---------|-------|-----------------|

| 1        | Switch  | 输入    | 开关切换电平输入        |

| 2        | Video-G | 输入    | 视频图像 G 信号输入     |

| 3        | PC-G    | 输入    | PC 图像 G 信号输入    |

| 4        | Gout    | 输出    | 图像 G 信号输出       |

| 5        | Video-R | 输入    | Video 图像 R 信号输入 |

| 6        | PC-R    | 输入    | PC 图像 R 信号输入    |

| 7        | Rout    | 输出    | 图像 R 信号输出       |

| 8        | GND     | 接地    | 地               |

| 9        | Bout    | 输出    | 图像 B 信号输出       |

| 10       | PC-B    | 输入    | PC 图像 B 信号输入    |

| 11       | Video-B | 输入    | Video 图像 B 信号输入 |

| 12、13、14 | 空       | 空     | 空               |

| 15       | GND     | 输入    | 输出允许端           |

| 16       | Vcc     | 输入    | 电源 5V           |

由倍行板输出的 Vi deo 图像信号 (R/G/B), 经由数字板上 J601 的第 6(G), 8(B), 10(R) 脚输入, 经过电容耦合及低通滤波 (R 通道由 C638, C641, R608, L613, C629 组成, G 通道由 C639, C642, R609, L614, C630 组成, B 通道由 C637, C640, R607, L612, C628 组成)后,分别输入到 U603 的第 5(R), 2(G), 11(B) 脚。当 CPU(U500)的第 40 脚输出为低电平(即选择 Vi deo 时), U603 的输入脚 5(R), 2(G), 11(B) 脚分别与其输出脚第 7(R), 4(G), 9(B) 连通,输入的 Vi deo 图像 R/G/B 信号即可由 U603 的第 7, 4, 9 脚输出。

由 PC 输入的 R/G/B 信号, 经由数字板 J600 的第 9 (R), 11 (G), 13 (B) 脚输入, 经过阻抗匹配及耦合电路 (R 通道由 D600, R604, C600 组成, G 通道由 D601, R605, C601 组成, B 通道由 D602, R606, C602 组成) 后,分别输入到 U603 的第 6 (R), 3 (G), 10 (B) 脚。当 CPU (U500) 的第 40 脚输出为高电平 (即选择 RGB-PC 时), U603 的输入脚第 6 (R), 3 (G), 10 (B) 脚分别与其输出脚第 7 (R), 4 (G), 9 (B) 连通,输入的 PC 信号即可由 U603 的第 7, 4, 9 脚输出。

由 U603 的第 7(R), 4(G), 9(B) 输出的图像信号输入到由 Q601(R), Q600(G), Q602(B) 形成射随器,由射随器进行驱动隔离后输出给后级的图像数字化电路(AD9883)进行 A/D 转换。

#### 同步信号 (SYNC) 切换选择电路

同步(SYNC)信号切换选择电路的主要任务是在由倍行板输出的同步(SYNC)信号和由 PC 输入的同步(SYNC)信号之间选择一个,输出给后级的图像数字化电路及图像处理电路。

从倍行板输出的行同步(HSYNC)信号经由 J601 的第 4 脚输入到数字板,通过电阻 R626 连接到 U600 的第 1 脚,场同步(VSYNC)信号经由 J601 的第 2 脚输入到数字板,通过电阻 R627 连接到 U600 的第 12 脚,当选择开关电平由 CPU(U500)的第 40 脚输出为高时,从倍行板输入的行同步(HSYNC)、场同步(VSYNC)信号分别从 U600 的第 3 脚(HSYNC)和第 13 脚(VSYNC)脚输出。

从 PC 输出的行同步 (PC-HSYNC) 信号由 J600 的第 7 脚输入,经过限幅 (D603) 后,通过 R603 连接到 U600 的第 5 脚,场同步 (PC-VSYNC) 信号由 J600 的第 5 脚输入到数字板,经过限幅 (D604) 及防抖动电路 (由 R602, R600 组成) 后,输入到 U600 的第 14 脚;当选择开关电平 (由 CPU (U500) 的第 40 脚输出为低时,从 PC 输入的行同步 (PC-HSYNC)、场同步 (PC-VSYNC) 信号分别从 U600 的第 3 脚 (HSYNC) 和第 13 脚 (VSYNC) 脚输出。

由 U600 的第 3 脚输出的行同步 (HSYNC) 信号通过电阻 R615 输入到反相器 U506 的第 13 脚, 然

后由 U506 的第 12 脚输出,通过电阻 R616 后再次输入到反相器 U506 的第 11 脚,再由反相器 U506 的第 10 脚输出。经过反相器 U506 两次反相后的行同步(HSYNC)信号恢复成了它原来的极性,同时也得到边缘整形,然后分成两路,一路经 R618 输出到图像处理芯片,另一路经 R619 输出到图像数字化芯片。

同样的,由 U600 输出声同步(VSYNC)信号,经过 R614 连接到 U506 的第 1 脚,经过两次反相(U506.1  $\rightarrow$  U506.2  $\rightarrow$  R610  $\rightarrow$  U506.3  $\rightarrow$  U506.4)后,分成两路,一路经 R611输出给图像处理芯片,另一路经 R617输出给图像数字化芯片。

#### 二,图像数字化电路

图像数字化电路的主要任务是将输入的图像经过 A/D 转换器(AD9883)的数字化采样,形成后级图像处理芯片能够处理的数字图像信号。

经过前级图像通道切换选择电路的选择,输入的纯图像信号经过 C632 (G), C634 (R), C636 (B) 的耦合后,输入到 A/D 转换器 (U302: AD9883) 的第 54 脚(R<sub>Ain</sub>),第 48 脚(G<sub>Ain</sub>),第 43 脚(B<sub>Ain</sub>)。

切换选择后的行同步(H<sub>SYNC</sub>)信号、场同步(V<sub>SYNC</sub>)信号通过防抖动电路(H<sub>SYNC</sub>通道由 R319, R317, C331 组成, V<sub>SYNC</sub>通道由 R320, R318, C332 组成)后,输入到 A/D 转换器(U302: AD9883)的第 30 脚(H<sub>SYNC</sub>)和第 31 脚(V<sub>SYNC</sub>)。

从 CPU (U500) 的第 8 脚 (CLK) 脚,第 9 脚 (DATA) 脚输出的 I<sup>2</sup>C 控制信号,被 Q301 (CLK),Q302 (DATA) 构成的电平转换电路进行电平转换后,通过电阻 R306,R307 (CLK 通过 R306,DATA 通过 R307) 连接到 A/D 转换器 (U302: AD9883) 的第 56 (SCL)、57 (SDA) 脚,对 A/D 转换器进行控制设定。

A/D 转换器(U302: AD9883)在 I°C 控制信号的控制下,同时根据输入的行场同步信号的频率及极性,以及第 33 脚输入的滤波值,将输入的行频信号分频成与输入图像变化频率相适应的采样时钟。另一方面,A/D 转换器(U302: AD9883)根据 I°C 控制信号设定的相位,钳位电平及增益等,按照新分频得到采样时钟频率对输入的模拟图像信号进行数字化采样,使输入的模拟图像信号变成数字图像信号。

数字化后的 R/G/B 图像信号分别从 A/D 转换器(U302: AD9883)中各自的通道中输出(R0 $^{\circ}$ R7: 第 77 $^{\circ}$ 70 脚; G0 $^{\circ}$ G7: 第 9 $^{\circ}$ 2 脚; B0 $^{\circ}$ B7: 第 19 $^{\circ}$ 12 脚),分别经排阻(R 通道: RP300, RP301; B 通道: RP302, RP305; G 通道: RP303, RP304)的缓冲后,输出给后级的图像处理芯片。

在 A/D 转换器内形成的时钟信号从 A/D 转换器的第 67 脚输出,经过滤波电路(由 R311, C323)的滤波后输出到后级的图像处理芯片的时钟输入端。

# 三, 数字图像缩放处理电路

数字图像缩放处理电路的主要任务是将由前级电路(A/D 转换器:图像信号数字化电路)送来的数字图像信号,按照 CPU(U500)的控制设定,经过一系列复杂的算法,最后输出具有固定行频、场频的数字图像信号,使其能在后级的 PDP 屏上正确显示。数字图像缩放处理电路具体由两块电路组成,一块负责数字图像信号的输入输出及缩放运算(U100: MX88L284AEC),另一块负责数字图像信号的数据暂存(由两块 16Mbit 的 SDRAM 组成,U400,U401,型号为 HY57V161610D)。

由前级 A/D 转换器(U302: AD9883)输出的数字 R/G/B 图像信号经由数字图像缩放处理芯片(U100: MX88L284AEC)上相对应的管脚(R0~R7: 19~12 脚; G0~G7: 10~3 脚; B0~B7: 28~21脚)输入到数字图像处理芯片。

数字图像处理芯片根据由其第 207 脚输入的时钟信号,第 203 脚输入的行同步( $H_{SYNC}$ )信号,第 204 脚输入的场同步( $V_{SYNC}$ )信号,将输入的数字图像信号一帧一帧地暂存到由 SDRAM 构成的暂存器中以备后续处理。

然后,数字图像处理芯片 MCU 通过三线串行通讯(SBCS:由 MCU (U500)的第 43 脚经电阻 R101 缓冲后连接到处理芯片 (U100)的第 183 脚;SBDATA:由 MCU (U500)的第 42 脚经电阻 R102 缓冲后连接到处理芯片 (U100)的第 184 脚;SBCLK:由 MCU (U500)的第 41 脚经电阻 R100 缓冲后连接到处理芯片 (U100)的第 185 脚)就输入的需要执行的设定 (即执行一定的算法),对已输入的数字图像信号进行处理。

有时,在将已处理的数字图像信号输出之前,处理芯片会根据需要将由其 OSD 引脚(OSD-R: 109 脚; OSD-G: 110 脚; OSD-B: 111 脚; OSD-BLANK: 112 脚; OSD-CLK: 104 脚; OSD-INT: 106 脚)输入的 OSD 字符信号嵌入到数字图像信号中去以方便用户对机器的使用。

已经过一系列算法处理的数字图像信号(有时会被嵌入 OSD 字符),按一定的规则(规定的时钟 频率、行频、场频等)从处理芯片输出(R0~R6: 98~92 脚; R7: 90 脚; G0~G7: 87~80 脚; B0~B7: 79~72 脚; H<sub>SYNC</sub>: 99 脚; V<sub>SYNC</sub>: 100 脚; Blank: 101 脚; LCKA: 70 脚); 经过一些缓冲(R/G/B 及 同步消隐信号的缓冲器件为排阻。R 通道: RP101, RP103; G 通道: RP102, RP105; B 通道: RP104, RP106; 同步 及消隐: RP108); 时钟信号的缓冲器件为感容滤波网络(由电容 C100, C101; 电感:; 100 构成))后,输出到 LVDS 传送器进行编码传送。

### 四,OSD 发生器电路:

OSD 发生器电路的主要任务是在 MCU 的控制下产生适当的 OSD 字符,以供图像处理芯片使用。由单片 OSD 发生器芯片 U601(TCL-CF2U1-MY)构成。

OSD 发生器芯片(U601: TCL-CF2U1-MY)在 MCU(U500)的 I<sup>2</sup>C 控制下(CLK 线: 通过由Q604 和 R621, R639, R641 组成的 I<sup>2</sup>C 时钟线隔离缓冲电路从 OSD 发生器芯片(U601)的第 8 脚连接到 MCU(U500)的第 8 脚; Data 线: 通过由Q603 和 R640, R642, R620 组成的 I<sup>2</sup>C 数据线隔离缓冲电路从 OSD 发生器芯片(U601)的第 7 脚连接到 MCU(U500)的第 9 脚。),同时根据由图像处理芯片所传来的行、场同步及时钟信号,实时地输出适当的 OSD 字符信号(输入的行、场同步及时钟信号的连接: 行同步(H<sub>SYNC</sub>)信号: U100 的第 99 脚——RP108 的第 7 脚——RP108 的第 8 脚——R714——RP700 的第 3 脚——U601 的第 5 脚; 场同步(V<sub>SYNC</sub>)信号: U100 的第 100 脚——RP108 的第 5 脚——RP108 的第 6 脚——R715——RP701 的第 8 脚——RP701 的第 7 脚——U601 的第 14 脚;时钟(CLOCK)信号: U100 的第 104 脚——U601 的第 2 脚; OSD-INT 信号: U100 的第 106 脚——R623——U601 的第 15 脚。由 OSD 发生器输出的 OSD 信号线的连接: RED(红色)信号: U601 的第 19 脚——RP601 的第 3 脚——RP601 的第 2 脚——U100 的第 110 脚; GREEN(绿色)信号: U601 的第 18 脚——RP601 的第 3 脚——RP601 的第 4 脚——U100 的第 110 脚; BLUE(蓝色)信号: U601 的第 17 脚——RP601 的第 7 脚——RP601 的第 8 脚——U100 的第 112 脚。

# 五,微控制器,存储器,按键,复位及 $I^2C$ 扩展部分:

微控制器 U500(MCU)的主要任务是根据人机界面(如按键、遥控等)输入的指令,控制整个系统的运行。存储器的主要任务是将系统在掉电情况下需要保存的数据存储起来而不会掉失,由一片  $E^2$ PROM(U502:24616)构成。复位电路的主要任务是在上电时刻使微控制器正确复位,由单片的 复位电路(U501:MAX810)构成。 $I^2$ C 增强电路的主要任务是将要进行较远距的  $I^2$ C 信号进行增强,使  $I^2$ C 线上的设备能正确接收  $I^2$ C 信号。按键主要功能是人机界面。

微控制器(U500: MCU)通过其第 8 脚(CLK)及第 9 脚(DATA)输出 I<sup>2</sup>C 信号,对具有 I<sup>2</sup>C 信号接口的芯片进行控制及通信。通过其第 43 脚(SBCS),第 42 脚(SBDATA)和第 41 脚(SBCLK)输出三线串行控制信号。对数字图像缩放电路进行控制。通过其第 28 脚输出高低电平开关信号,通过 Q501, R519, R516 组成的缓部驱动电路控制系统工作电源的开启/关闭。通过其第 40 脚输出切换信

号去控制视频切换开关(U603)及同步切换开关(U600)。通过其第 2~7 脚输出信号对键盘进行扫描,以获得使用者的指令。

存储器(U502: 24C16)通过其第 5 脚(DATA)和第 6 脚(CLK)连接到  $I^2$ C 总线上,接收从  $I^2$ C 总线上传来的数据并将其存储起来。

复位电路(U501: MAX810)在上电时由其第2脚输出复位信号到微控制器(U500)的第16脚,对微控制器进行复位。

I<sup>2</sup>C 扩展增强电路由 U503 及 U505(82B715)构成。

#### 六,LVDS 传送器:

LVDS 传送器的主要任务是将由数字图像缩放电路传来的数字图像信号进行 LVDS 编码,并将编码后的信号传送给远端的 PDP 屏进行显示。由单片的 LVDS 传送器芯片(U705: DS90C383A)构成。

由数字图像缩放电路传来的数字图像信号经过缓冲后传送到 LVDS 传送器(R0~R7: U705 的第 16, 18~25 脚; G0~G7: U705 的第 6~15 脚; B0~B7: U705 的第 51, 52, 54, 55, 56, 2, 3, 4 脚; 消隐信号(BLANK): U705 的第 27 脚; 行同步信号( $H_{SYNC}$ ): U705 的第 28 脚; 场同步信号( $V_{SYNC}$ ): U705 的第 30 脚; 显示允许信号(Display Enable): U705 的第 50 脚; 时钟信号(CLK): U705 的第 31 脚),经过 LVDS 传送器的适当编码,然后以符合 LVDS 信号规则的形式从 LVDS 传送器(U705)中  $T_{X}$ 0-(第 48 脚), $T_{X}$ 0+(第 47 脚), $T_{X}$ 1-(第 46 脚), $T_{X}$ 1+(第 45 脚), $T_{X}$ 2-(第 42 脚), $T_{X}$ 2+(第 41 脚), $T_{X}$ 3-(第 38 脚), $T_{X}$ 3+(第 37 脚), $T_{X}$ 4 (第 40 脚), $T_{X}$ 5 (第 39 脚),通过 LVDS 传输线缆传输出远端的 PDP 屏进行显示。

通讯板的主要任务是接收从机顶盒传来的数字视频信号并将其传送给 PDP 屏进行显示,同时对 PDP 屏上的电源进行控制及对输入的遥控及按键信号进行解码并传送给机顶盒。

### 一,LVDS 信号接收解码器:

LVDS 信号接收解码器的主要任务是接收从机顶盒经 LVDS 传输线缆传来的经过 LVDS 传送编码器编码的数字视频信号,然后将其解码成 LVTTL 电平格式的各种彩色信号分离的数字视频信号,由单片 LVDS 接收解码芯片(U1: DS90CF384AMTD)构成。

由 LVDS 传输线缆送来的 LVDS 信号经由通讯板接口端的 25 针 D 型插座(J3)输入到通讯板,经过 LVDS 信号中各对信号相对应的匹配电阻后输入到 LVDS 信号接收解码器(U1:DS90CF384AMTD)。LVDS 信号的连接方式为: $R_X0$ -: J3 的第 14 脚→U1 的第 9 脚; $R_X0$ +: J3 的第 2 脚→U1 的第 10 脚; $R_X1$ -: J3 的第 3 脚→U1 的第 11 脚; $R_X1$ +: J3 的第 16 脚→U1 的第 12 脚; $R_X2$ -: J3 的第 17 脚→U1 的第 15 脚; $R_X2$ +: J3 的第 5 脚→U1 的第 16 脚; $R_X3$ -: J3 的第 20 脚→U1 的第 19 脚; $R_X3$ +: J3 的第 8 脚→U1 的第 20 脚; $R_X$ CLK-: J3 的第 6 脚→U1 的第 17 脚; $R_X$ CLK+: J3 的第 19 脚→U1 的第 18 脚; $R_X3$ 1 为  $R_X0$ 1 线对的匹配电阻; $R_X1$ 2 线对的匹配电阻; $R_X1$ 3 为  $R_X1$ 3 线对的匹配电阻; $R_X1$ 3 为  $R_X2$ 3 线对的匹配电阻; $R_X1$ 3 为  $R_X2$ 4 线对的匹配电阻; $R_X1$ 4 为  $R_X3$ 3 线对的匹配电阻; $R_X1$ 5 为  $R_X1$ 6 线对的匹配电阻; $R_X1$ 6 线对的匹配电阻; $R_X1$ 7 线对的匹配电阻; $R_X1$ 7 线对的匹配电阻; $R_X1$ 8 线对的匹配电阻; $R_X1$ 9 线对的压阻

以 LVDS 信号编码的数字视频信号输入到 LVDS 接收解码器(U1: DS90CF384AMTD)后,经 LVDS 接收解码器的解码并恢复成 LVTTL 电平格式的各种彩色信号分离的数字视频信号,从 LVDS 接收解码器的相应端口输出,经排阻缓冲后传输出电平转换及驱动电路。

#### 二, 电平转换及驱动电路:

电平转换及驱动电路的主要任务是将从 LVDS 接收解码器输出的 LVTTL 电平的数字视频信号转换成 TTL 电平的数字视频信号并增强驱动能力,由四块 74HCT541(U2,U3,U4,U5)组成。

R 信号由 U3 进行电平转换及驱动(R0~R7: 由 U3 的第 9~2 脚输入,由 U3 的第 11~18 脚输出); G 信号由 U2 进行电平转换及驱动(G0~G7: 由 U2 的第 9~2 脚输入,由 U2 的第 11~18 脚输出); B 信号由 U4 进行转换及驱动(B0~B7: 由 U4 的第 9~2 脚输入,由 U4 的第 11~18 脚输出); 其余信号(行、场同步,消隐,时钟,显示使能等)由 U5 进行电平转换及驱动(显示使能(Display-Enable)信号由 U5 的第 2 脚输入,由 U5 的第 18 脚输出; H<sub>SYNC</sub>信号由 U5 的第 4,5 脚输入,由 U5 的第 15,16 脚输出; V<sub>SYNC</sub>信号由 U5 的第 6,7 脚输入,由 U5 的第 13,14 脚输出; CLK 信号由 U5 的第 8,9 脚输入,由 U5 的第 11,12 脚输出;消隐信号(BLANK)由 U5 的第 2 脚输入,由 U5 的第 17 脚输出。)经过电平转换及驱动后的数字视频信号经过插座(J4)及连接线后传输给 PDP 屏,以供显示。

# 三, 微控制器复位, I<sup>2</sup>C 增强驱动, 按键及遥控:

微控制器(U9: MTV212MN32)的主要任务是接收机顶盒通过  $I^2C$  总线传来的控制命令,然后按控制命令执行开关机,同时完成 PDP 屏上电源故障态的检测,按键及遥控器信号的解码,并将其反馈给机顶盒。

微控制器(U9: MTV212MN32)的第 12 和 22 脚输出信号控制 PDP 屏电源的开/关(通过 Q1 和 Q2 的驱动);第 26 脚和 27 脚作为 PDP 屏电源故障检测输入脚;第 28 脚为运行指示灯(绿灯)的控制输出;第 29 脚为待机指示灯的控制输出;第 24 (HSCL)、25 (HSDA) 脚分别连接到  $I^2$ C 总线的 CLK 和 DATA 线,接收通过  $I^2$ C 总线送来的命令和传送已经解码的按键遥控命令以及检测到的电源故障态;第 15 脚输入遥控信号进行解码;第 13,14,16,17 脚输出信号扫描按键矩阵及获得按键的状

态。

复位电路的主要任务是在上电时刻使微控制器正确复位,由单片的复位电路(U8: MAX810)构成。在上电时刻输出复位信号到微控制器(U9: MTV212MN32)的第 4 脚,对微控制器(U9)进行复位。

$I^2C$  增强驱动电路的主要任务是将要进行远距离传输的  $I^2C$  信号进行增强,以利于接收。由 U6 和 U11 (82B715) 构成,串接在  $I^2C$  总线上。

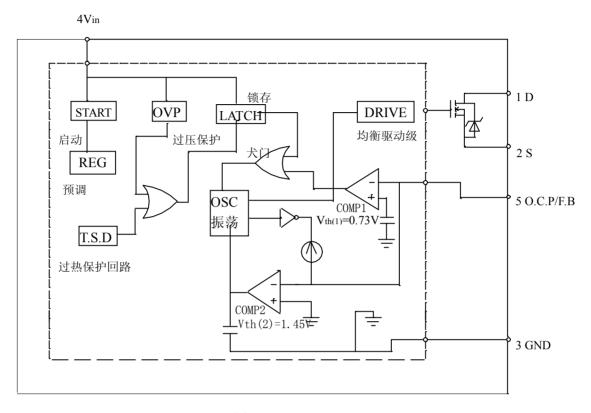

# 一,概述

TCL 王牌 PDP403 等离子电视机顶盒的开关电源是以混合集成电路 STR-G6653 为主组成电流反馈控制调频式开关电源。在 STR-G6653 (IC801) 中包含大功率开关 MOS 管和一个驱动控制电路。STR-G6653 集成电路的内电路方框图如 7.1 所示。

图 7.1

#### 其主要特点为:

- 一、为小型5脚二排成型塑料封装,其外部为绝缘塑料,无需绝缘套管和云母片。

- 二、外围元件很少,电路简单,只需加入少量元件,就可以组成一个典型的开关电源。

- 三、待机状态功耗很小,节省能源。(约1.5W)。

- 四、具有多种电源保护功能,其中包括脉冲过流保护,具有锁定装置的过压保护、过热保护。

- 五、准谐振工作模式,减少 EMI 辐射。

# STR-G6653 集成电路各引出脚功能(表 7.1)

表 7.1 STR-G6653 各引出脚功能

| 引出脚 | 符号              | 说明       | 功能                |

|-----|-----------------|----------|-------------------|

| 1   | D               | 漏极       | 功率 MOS 管的漏极       |

| 2   | S               | 源极       | 功率 MOS 管的源极       |

| 3   | GND             | 接地       | 内部接地端             |

| 4   | V <sub>IN</sub> | 电压输入     | 控制电路电源输入          |

| 5   | O.C.P / F.B.    | 过流保护/反馈端 | 过流敏感信号输入/稳压控制信号输入 |

#### 二, STR-G6653 集成主要引出脚功能介绍

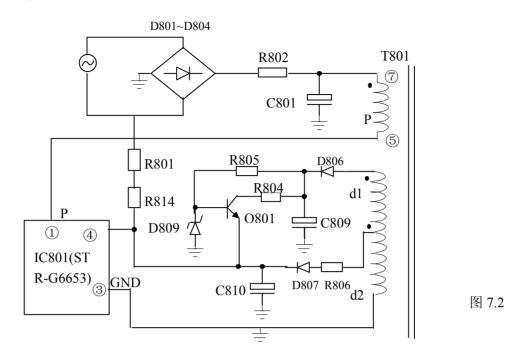

1、④脚  $V_{IN}$ 输入端:接开关电源的启动电路。开关电源的启动电路原理图如图 7.2 所示。

启动电路根据④脚电压的大小,确定启动电路开始工作或者停止工作。典型工作电压为 16V。D806、D807 为整流二极管。C809、C810 为滤波电容。R801、R814 为启动电阻。当打开电源开关后,交流电通过 R801、R814 为 C810 充电,当④脚电压达到 16V 时,启动电路开始工作。当控制电路开始工作。当控制电路开始工作后,d1,d2 绕组两端产生感应电压,整流二极管 D806、D807 工作,并对 C809、C810 充电。其中 d1 绕组为待机用电源绕组,提供待机工作时  $V_{\rm IN}$ 输入,d2 绕组为正常工作时电源绕组,提供正常工作时  $V_{\rm IN}$ 输入。由于正常工作时 C809 两端电压约 100V,经过 R805 及 D809 稳压,使 Q801 B 极为 16V,而 Q801 的 E 极也为 16V,所以 Q801 截止。结果④脚由 D807 经 C810 滤波形成稳定的 16V电压供给。维持控制电路的正常工作。而当处于待机状态时,因 D807 输出电压低于 16V,此时,Q801 的 B 极仍为 16V,Q801 导通,经 B-E 结向④脚提供电压。实现了待机状态下启动电路的工作电压。

考虑到在低电压(90V)的启动电流也应≥500uA,启动电阻 R801、R814 不宜取得太大,但也不宜太小。参考资料为 82K~150K Ω。所以 R801、R814 分别为 51K。C810 的参考值为 47uF~100uF。因为电容太小,会造成电压跌落很快,太大会造成起动充电时间长。启动电路中 R、C 元件,在更换时要注意。

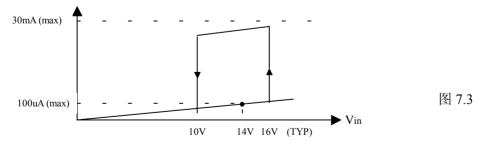

图 7.3 为④脚输入电流与输入电压的关系。

由图 7.3 可知,控制电路起动前,即  $V_{IN} \le 14V$  时,输入电流最大为 100uA。当  $V_{IN}$ 达到 16V 时,工作电流开始增大,当电压减少到 10V 时,内部电路停止工作,返回到启动模式。

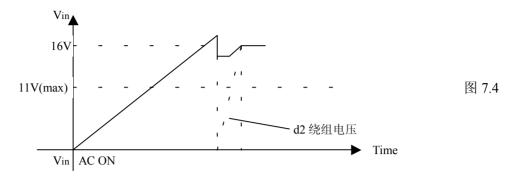

图 7.4 为 V<sub>IN</sub> 端电压起动波形

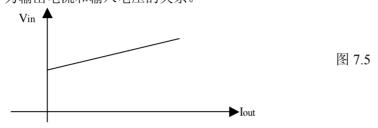

电源启动电路工作后,④脚电压线性增加,其增长速率取决于启动电阻和电容(R801、R814、C810)。当④脚电压达到16V时,D806、D807导通,④脚电压由D807整流,C810滤波后提供。图 7.5 为输出电流和输入电压的关系。

由图可知,随着输出电流增加,变压器中激励电流增加, $V_{\rm IN}$  略有上升。当开关管关断瞬间,绕组中会产生冲击电压,这个冲击电压通过绕组 d2,经 D807、C810 使  $V_{\rm IN}$  电压异常,为了防止此现象,可以象图 7.2 中所示,在 D807 中串联 R806 电阻,防止冲击电流的影响。

#### 2、O.C.P/F.B 脚

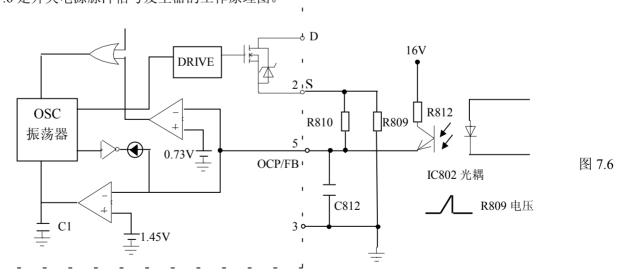

先说振荡器和稳压控制电路。振荡器产生使开关管导通与关断的脉冲信号,脉冲信号的形成由集成内部的 C1 充放电过程完成。根据开关电源的稳压原理,稳压过程受开关管导通截止时间的控制,图 7.6 是开关电源脉冲信号发生器的工作原理图。

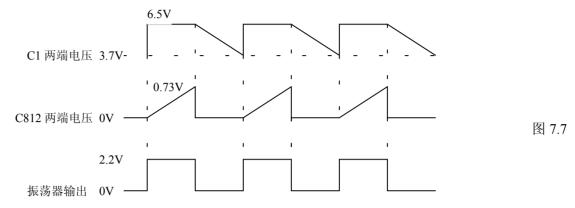

首先分析没有光耦反馈信号输入的情况。此时相当于外围只有 R809、R810、C812 三个元件。当 MOS 管处于 ON 时,C1 充电到固定电压 6.5V。另一方面,工作电流  $I_D$  流过 R809 到地脚。此电流波形为一个锯齿状,所以在电容 C812 两端的电压波形为锯齿状。(下面有波形说明)。此电压通过 R810 接到 IC 的⑤脚 O.C.P/F.B 端。当⑤脚的电压达到阈值  $V_{th(1)} \approx 0.73$ V 时,比较 1 输出低电平,MOS 管 OFF 状态。当 MOS 管处于 OFF 状态后,C1 的电荷开始释放,当电压下降到 3.7V 时,振荡器输出反

相, MOS 管又处于 ON, 处于 C1 迅速充电到 6.5V, 反复处于 ON 与 OFF 状态。由以上分析, MOS 处于 ON 的脉宽(时间)由 R809 决定, 而 OFF 的脉宽(时间)由 C1 放电时间决定。

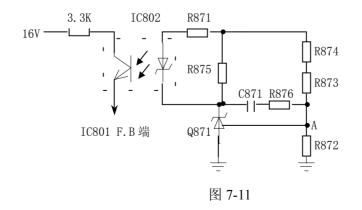

当输出反馈信号 F.B 电流通过 R812 和光耦 IC802, ⑤脚 O.C.P/F.B 上的电流为  $I_D$  的电流叠加光耦流过的电流。由下图可知,当电流变化时,MOS 管 ON 与 OFF 时间的改变。开机状态和待机状态的控制就是以此原理来实现。

由上图可知,当电流较大时,电压上升速率比较快。当电流较小(负载比较轻)时,电压上升率较慢。本机型的待机状态和开机状态就是利用⑤脚 的反馈电流不一样大的原理来实现。在待机状态时的反馈电流比正常开机的电流大。

一般地,在待机状态负载轻,FB 的电流比较小,为防止在 MOS 管 OFF 状态时产生的浪涌影响比较器 1 的工作,在 IC 设计时增加一个 1.35mA 的恒流源。另 C812 可吸收 MOS 管 ON 时的噪声。

过流保护就是检测在每个脉冲周期  $I_D$  的峰值电流,也就是检测  $R809(2W,0.33\,\Omega)$ 上的电流。过流保护的阈值电压为 0.73V,当副边电路出现过流现象时,原边的  $V_{IN}$  端电压会下降,当  $V_{IN}$  电压降到低于锁存关闭电压(10.5V)时,控制电路停止工作,从而实现过流保护。

#### 三, STR-G6653 混合集成电路在 TCL 王牌 PDP403 机顶盒的应用

TCL 王牌 PDP403 机顶盒采用以 STR-G6653 的开关电源, 其应用电路图可参考原理图。

#### 1, 开关电源工作原理简述

220V/50Hz 的交流电源电压经过电源开关 S800 及 R801A、C801、RV801、LF801、C802、LF802 等组成的抗脉冲干扰网络,进入由 D801、D802、D803、D804 组成的桥式整流电路,整流后的脉冲电压再经防冲击电阻 R802 及 C805、C811 平滑滤波,加到 T801 的初级绕组的第⑦脚。由第⑤脚进入IC801 的①脚接内部 MOS 管的 D 极。与此同时,电源输入端交流电压经 R801、R814 对 IC801 的④脚外接电容 C810 充电,开关电源开始启动,启动电路的工作原理见图 7.2。当④脚的电压达到 16.0V 时,完成了启动,同时经过预调整电路,使开关电源的振荡电路开始工作。脉冲振荡压经 IC801 内驱动电路,由内接到开关管的栅极。在开关脉冲作用下,开关管时而导通,时而截止。在开关变压器的次级绕组上感应出的脉冲电压,经过不同的整流、滤波电路,分别输出+33V、+26V、+12V、+5V、+5V 待机电压、-20V 等 6 个不同直流稳压电压,供给机顶盒各部分使用。

其中: +33V 直流电压供待机时降到 6.5V 使用;

+12V 直流电压经稳压为 8V 后,供图像、伴音信号处理等各部分使用;

- +5V 直流电压供数字板使用。

- +5V 待机直流电压供 CPU 使用;

- +26V 直流电压供伴音功放电路使用。

- -20V 直流电压供伴音功放, 防关机冲击声使用。

#### 稳压过程:

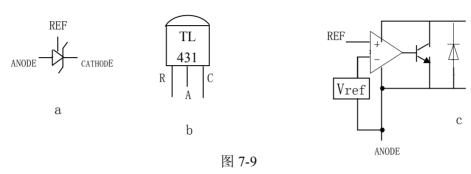

先简单介绍 TL431 的使用。TL431 是一个有良好热稳定性的三端可调分流基准源,它的输出电压用两个电阻就可以任意地设置为从  $V_{ref}$  (2.5V) 到 36V 范围内的任何值。下图 a 为该器件的符号,3个引出脚分别为:阴极(cathode)、阳极(anode)和参考端(Ref.)。b 为外形图,c 为 TCL431 的内部示意图。

#### 恒压电路的应用:

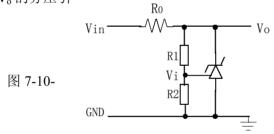

在 TL431 的内部含有一个 2.5V 的基准电压,所以当在 Ref 引入输出反馈时,器件可以通过从阴极到阳极很宽的范围的分流,控制输出电压。如下图所示的电路中,当 R1 和 R2 的阻值确定时,两者对  $V_0$  的分压引 入反馈。

若  $V_o$ 增大,反馈量增大,TL431 的分流也就增大,从而又导致  $V_o$ 下降。显然,这个深度负反馈电路必然在  $V_i$ 等于基准电压时处稳压。此时, $V_o$ =(1+R1/R2)•  $V_{ref}$ 。选择不同的 R1 和 R2 的值,就可以得到 2.5~36V 范围内的任意电压。特别地,当 R1=R2 时, $V_o$ =5V。需要注意的是,在选择电阻时,必须保证 TL431 工作的必要条件,就是通过阴极的电流要大于 1mA。

本机型使用 TL431 构成的稳压电路。

当  $V_{IN}$  (5V) 升高时,由 R874、R873、R872 组成的分压电路,A 点电压升高,Q871 的分流增强,光耦导通程度增强,接到⑤脚 F.B 电流增大,IC 输出脉冲时间缩短,电压降低,最终稳压在 Ref 电压。所以  $V_o=V_{ref}$  [1+(R874+R873)/R872] =2.5[1+(22k+5.6k)/27k]=5V

#### 一、过热保护

IC801 内电路中设有过热保护电路。当集成电路内的 MOS 管的结温度超过 150℃ (典型值) 时,过热保护电路通过锁存电路使驱动器停止工作,开关脉冲无输出,开关电源停止工作。

#### 二、过压保护

在 IC801 集成电路内,同样设有过压保护电路。当交流电压过高时,通过开关变压器 T801 中的 初级绕组的电压上升,启动绕组 d1 的电压上升,引起 C810 两端电压上升, $V_{\rm IN}$ 增加,超过一定门限 电压后(20.5V),过压保护电路起作用,通过或门电路和锁存电路,使驱动器停止工作,起到保护作用。

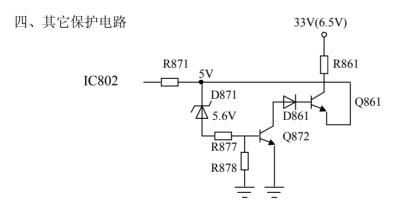

#### 三、待机状态

从电原理图可以看出,当 P805 插座的 power 开关信号处于高电平时,Q862 导通,Q861 截止,电路处于正常工作状态。当 power 开关处于低电平,Q862 截止,Q861 导通,电路处于待机状态,此时 33V 输出只有 6.5V,其它电压也相应地降低。下表为开机与待机之间各电压的变化。

| 各 电 压  | 开机状态 | 待机状态  |

|--------|------|-------|

| +33V   | 33V  | 6.5V  |

| +26V   | 26V  | 5.8V  |

| +12V   | 12V  | 2.0V  |

| +5V    | 5V   | 1.0V  |

| +5V 待机 | 5.0V | 5.0V  |

| -20V   | -20V | -4.0V |

图 7-12

从电原理图 D871、R877、R878、Q872 等组成在待机状态下,当控制环路存在断路现象时起保护作用。工作原理如下:当待机状态下,反馈电流比较大,此时输出的电压较开机低。如果反馈环路断路,反馈电流减少,输出电压马上升高。当 5V 电压升高到 5.6V 时,D871 导通,Q872 导通。此时,相当于机器处开机状态。(相当于 Q862 导通),Q861 截止,避免因电压过高而将 R862 烧坏,影响待机的正常工作。当开机状态下存在控制环路断路,由于电压升高,则同时  $V_{\rm IN}$  也升高,当  $V_{\rm IN}$  大于 20.5V 时,集成内部过压保护电路起作用。

# 第八章 显示屏安装指导

安装环境: 无尘工作室。

**安装工具:**螺丝刀、风劈、剪钳、工具刀(开箱、卸包装)、镜头布、海面垫、白手套(必须佩带、选质地较软的)

#### 安装步骤:

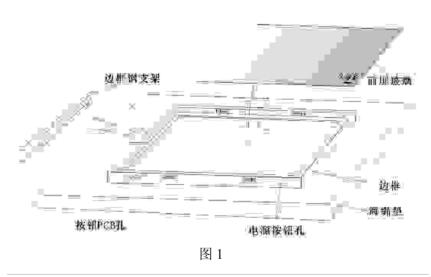

#### 1, 安装边框:

首先,找出边框物料,在面积较大的平整工作台上铺上海绵垫,将边框放与垫子的中央。注意:槽口向上。检查边框,然后放在海绵垫上。如图(1)所示。

# 2, 安放前滤光玻璃:

撕掉前屏滤光玻璃上的保护纸,将玻璃放进边框。撕掉玻璃上的保护膜后手不能再触到玻璃。 要求: 在贴有印刷纸条的一面对向边框下边的电源按钮: 放置玻璃要正好卡在边框沟槽内。

#### 3, 边框支架条安装:

将边框支架条放进边框,打好螺钉。

要求: 放置支架条时, 注意长短边方向;

注意数量: 边框  $2 \uparrow$ ,顶框  $1 \uparrow$ ,底框  $1 \uparrow$ ;要打螺钉数量:  $22 \uparrow$ 打螺钉力矩要求在: 5—7kgf.cm;

#### 4, 安装 PDP 显示屏:

先抬出 PDP 显示屏, 撕掉屏上的保护膜, 将屏对准边框上的相应位置轻轻放下; 然后垂直打下屏上的螺钉。

要求: 撕掉屏上的保护膜后手不能再触到玻璃;

放置屏的位置时,应注意,上下方向;

要安装的元件数量: 屏四角螺钉 4个(4x16), 支架上螺钉 6个(4x16);

屏四角上紧固螺钉的力矩: 6—8kgf.cm; 屏支架上的紧固螺钉的力矩: 13—16kgf.cm; 注意,安装是不能将螺钉漏在 PDP 电路内,会发生短路。

5, 电源板安装检查: 找出电源板, 查看连接器, 和连接线。

要求: 板上数量: 6P 300 (6 针 300mm)、6P 1000、8P 150、8P 100、6P 500、6P 600、4P 250 的 连接线各一个。

#### 6, 电源按钮安装检查:

找到电源按钮板,将按钮开关 s/w 按图所示插到板上。

要求: 电源按钮板一个、电源按钮一个。

图 2

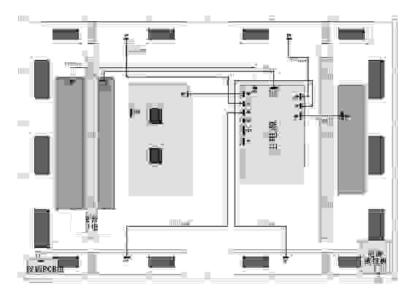

# 7, 电源板安装: 按图(2)所示

在安放电源板前先找到电源下的绝缘垫纸,放在电源板处,再放置电源板,用螺钉固定8个点。安装要求:数量:电源板1个、螺钉8个(3x8),

放置板时要注意板子的方向;

打螺钉的力矩要求: 6—8kgf.cm;

注意,不能把螺钉掉在,屏内。

#### 8, 通讯、控制板连接:

将通讯、控制板放在相应位置,用螺钉固定3个点。

最后将带有磁环的连接器(41P)将其与模块控制电路相连。

9, 安装电源滤波器、前控板、电源开关板:

将各板放置在相应的位置, 打上螺钉共7个(普通螺纹钉3x8; 自攻钉3x12)。

要求: 查看数量: 电源滤波器 1 个、底部按钮板 1 个、电源开关板 1 个、螺钉 7 个、地线螺钉 1 个 (4x8);

电源滤波器上固定 2 个、底部按钮板 2 个(这 2 个为自攻钉)电源开关板 3 个(其中 2 个自攻钉);

打螺钉的力矩要求: 6—8kgf.cm;

注意,不能把螺钉掉在里面。

### 10. 连线:

通讯、控制板 J1——电源板 J2;

通讯、控制板 J2——电源板 J3;

通讯、控制板 J5——前控板;

电源滤波器 P802/P803——电源开关板 P801

电源滤波器 P801——电源开关板 P802;

电源滤波器 P806/P807——电源板 J1;

电源板 J12----PDP 屏 P102;

电源板 J11——PDP 屏 P14; 电源板 J10——PDP 屏 P15; 电源板 J5——PDP 屏 P304; 电源板 J6——PDP 屏 P302; 电源板 J7——PDP 屏 P300; 电源板 J8——PDP 屏 P301; 电源板 J9——PDP 屏 P303;

# 11. 扎线:

扎线要求简洁、明快(可以根据工厂 PE 自定)。

- 12. 安装 A/V 端子盖板、PDP 后盖板:

- a: 安装 A/V 端子盖板。

要求: RGB/控制端子螺钉 2 个 (3x12); 电源端子螺钉 2 个 (3x8), 共有 4 个。 打螺钉的力矩要求: 6—8kgf.cm; 注意, 不能把螺钉掉在, 屏内。

b: 安装 PDP 后盖。

要求: 自攻螺钉 14 个 (4x16); 螺纹螺钉 2 个 (4x6); A/V 端子旁的后盖螺钉 8 个 (3x8), 共有 24 个。

打螺钉的力矩要求: 11—13kgf.cm。

13. 安装 PDP 底座与音响:

将底座接到 PDP 上, 打上 4 个螺钉。找出音箱,将其固定好。

注: 台式脚架、音箱、挂墙架、软胶条直接可以辨认,不再说明。

# 第九章 调试说明

#### 一、 概述:

PDP403 整机包括显示屏(主机)、机顶盒、音箱组件等,因接口板已更改,主机(显示屏)不能单独工作,必须与机顶盒相连才可正常工作。显示屏除接口板及电源外其它部分与 PDP402 大致相同;机顶盒通过 LVDS 接口与显示屏相连,具有电脑输入接口,DVD 分量接口,TV、AV 常规接口等,电脑显示格式支持 VGA(640×480/60Hz) XGA(1024×768/75Hz),TV 采用 PHILIPS 一体化频率合成高频头及解码 IC TDA9321,支持 PAL、NTSC、SECAM 彩色制式,逐行处理采用 NDSP 60Hz 逐行方案(NV320),SCALER 处理 IC 为旺宏 MX88L284ACE,丽音处理 IC 采用微科 MSP3410,件音制式支持 D/K、I、BG;音箱部分与 PDP402 完全相同。

#### 二、 调试内容及方式:

主机(显示屏)须调整电源电压及白平衡,工厂设置的进入方法为:当音量为0时按住机顶盒上音量减键不放,再快速按遥控器上数字键9、5、1,即可进入工厂设置;生产线调试时,可先进入工厂设置将第3页"MODE"项设为"02",则直接按遥控器上快捷键(音量键斜上方)可进入工厂设置,但出厂前必须将此项设为"00"。

#### 1. 电源部分调试

本机型电源调试一共有四个调试点,分别是 Va、Vs、Vsc、和 Vset up 。此四个电压值的要求已标示在每一台显示屏的右上角,根据规定的电压调试。

#### 调试方法如下:

将显示屏与机顶盒相连,输入白场信号,机器预热 15 分钟后,将图象对比度、亮度设为最大,分别进行以下四个电压的调整:

Va 值的调整: 数字万用表的红笔棒接 J8 或 J9 的第 1 脚, 黑笔棒接地, 调整 R78 (Va Adj) 电位器, 使数值与标称电压值相符, 误差为±0.5V。

Vs 值的调整: 数字万用表的红表棒接 J11 的第 9 脚,黑笔棒接地,调整 R183 (Vs Adj) 电位器,使数值与标称电压值相符,误差为±0.5V。

Vsc 值的调整: 数字万用表的红表棒接 J10 的第 2 脚, 黑笔棒接地, 调整 R245 (Vsc Adj) 电位器, 使数值与标称电压值相符, 误差为±0.5V。

Vset up 值的调整: 数字万用表的红表棒接 J10 的第 1 脚, 黑笔棒接地, 调整 R226 (Vset up Adj) 电位器, 使数值与标称电压值相符, 误差为±0.5V。

#### 2. 白平衡调整 (至少须预热 30 分钟以后进行):

本机须分别对 TV、PC 两种模式的白平衡进行调整,每种模式需要调两种色温: 低色温 9300K+8MPCD(x=0.284, y=0.299),高色温 11000K+10MPCD(x=0.265, y=280),另外,因显示屏内已无接口板,故调完白平衡后要做好白平衡数据记录,机顶盒必须与显示屏——对应编号,成品入库时也需要做好标记,显示屏与机顶盒——配套销售。具体调整方法如下: (1) TV 模式调整

#### A. 低色温调整 (9300K+8MPCD)

从白平衡测试仪输入黑白场信号,将画面置于标准状态,调整白平衡仪使暗场亮度为  $4^{\circ}$ 5nit,白场亮度为  $80^{\circ}$ 90nit,然后进入工厂设置第 1 页白平衡调整项,将低色温状态红色驱动电平(R-G93)设为 80,红色截止电平(R-C93)设为 90,先用色温计监测暗场区域,调整低色温状态绿、蓝截止电平(G-C93、B-C93)使白平衡仪的读数为 x=0.  $284\pm0$ . 010, y=0.  $299\pm0$ . 010, 再监测白场区域,调低色温状态绿、蓝驱动电平(G-G93、B-G93)使白平衡仪的读数为 x=0.  $284\pm0$ . 010, y=0.  $299\pm0$ . 010, 反复调整 1 到 2 次,使白场、暗场色温坐标均符合要求。

#### B. 高色温调整(11000K+10MPCD)

调整完低色温后,再将高色温状态红色驱动电平(R–G11)设为 80、红色截止电平(R–C11)设为 90,用色温计监测暗场区域,调整高色温状态绿、蓝截止电平(G–C11、B–C11)使白平衡仪的读数为 x=0. 265±0. 010,y=0. 280±0. 010,再监测白场区域,调高色温状态绿、蓝驱动电平(G–G11、B–G11)使白平衡仪的读数为 x=0. 265±0. 010,y=0. 280±0. 010,反复调整 1 到 2 次,使白场、暗场色温坐标均符合要求。

#### (2) PC 模式白平衡调整

#### A. 低色温调整

选择到 PC 模式,用电脑信号发生器输入灰度信号,调整对比度、亮度使灰度信号第三级亮度为  $4^{\circ}$ 5nit、倒数第三级亮度为  $80^{\circ}$ 90nit,然后进入工厂设置第 7 页 PC 白平衡调整项,将低色温状态红色驱动电平(PR-G93)设为 80,红色截止电平(PR-C93)设为 90,先用色温计监测第二级灰度,调整低色温状态绿、蓝截止电平(PG-C93、PB-C93)使白平衡仪的读数为 x=0. 284+0. 010,y=0. 299+0. 010,再监测倒数第二级灰度,调低色温状态绿、蓝驱动电平(G-G93、B-G93)使白平衡仪的读数为 x=0. 284+0. 010,y=0. 299+0. 010,反复调整 1 到 2 次,使白场、暗场色温坐标均符合要求。

#### B. 高色温调整(11000K+10MPCD)

调整完低色温后,再将高色温状态红色驱动电平(R-G11)设为 80、红色截止电平(R-C11)设为 90,用色温计监测第二级灰度,调整高色温状态绿、蓝截止电平(G-C11、B-C11)使白平衡仪的读数为  $x=0.265\pm0.010$ , $y=0.280\pm0.010$ ,再监测倒数第二级灰度,调高色温状态绿、蓝驱动电平(G-G11、B-G11)使白平衡仪的读数为  $x=0.265\pm0.010$ , $y=0.280\pm0.010$ ,反复调整 1 到 2 次,使白场、暗场色温坐标均符合要求。

#### 三、工厂菜单说明:

工厂设定数据除白平衡外,其它一般不用再调整,整机出厂前须检查是否与下列参考值一致。(带"★"项不用调整)

| 第1页(      | 进入工厂局 | f按数字键 1)TV/AV 白平衡调整  |

|-----------|-------|----------------------|

| R-G93     | 80 ★  | 低色温 9300K 红色驱动电平     |

| G-G93     | 6B    | 低色温 9300K 绿色驱动电平     |

| B-G93     | 70    | 低色温 9300K 蓝色驱动电平     |

| R-C93     | 90 ★  | 低色温 9300K 红色截止电平     |

| G-C93     | 83    | 低色温 9300K 绿色截止电平     |

| B-C93     | 78    | 低色温 9300K 蓝色截止电平     |

| R-G11     | 80 ★  | 高色温 11000K 红色驱动电平    |

| G-G11     | 7B    | 高色温 11000K 绿色驱动电平    |

| B-G11     | 60    | 高色温 11000K 蓝色驱动电平    |

| R-C11     | 90 ★  | 高色温 11000K 红色截止电平    |

| G-C11     | 80    | 高色温 11000K 绿色截止电平    |

| B-C11     | 7A    | 高色温 11000K 蓝色截止电平    |

| 第2页       |       | 动态低音增强               |

| W_FREQ    | 28 ★  | 重低音通道转折频率调整(步长 10Hz) |

| W_HP      | 02 ★  | 重低音通道附加高通滤波器选择       |

| W_LEVE    | 00 ★  | 重低音增强幅度              |

| M_STR     | 50 ★  | 动态低音效果增强调整           |

| $M_{HMC}$ | 0D ★  | 低音和声控制               |

| $M_{HP}$  | 07 ★  | 高通转折频率               |

| M_LP    | 0C ★ | 低通转折频率                   |

|---------|------|--------------------------|

| $M_LIM$ | F0 ★ | 低音幅度限制                   |

|         |      |                          |

| 第3页     | 伴音曲线 | 调整                       |

| V05     | 48 ★ | 音量刻度 0-5 段对应的音频输出幅度      |

| V25     | 6D ★ | 音量刻度 5-25 段对应的音频输出幅度     |

| V50     | 75 ★ | 音量刻度 25-50 段对应的音频输出幅度    |

| VMAX    | 7F ★ | 音量刻度 50-100 段对应的音频输出幅度   |

| SHARP   | 80 ★ | TV/AV 锐度控制               |

| MODE    | 00 ★ | 功能设定(注)                  |

| DKDB    | 33 ★ | D/K 制伴音输出幅度调整            |

| IDB     | 0C ★ | I制伴音输出幅度调整               |

| PHASEP  | 00 ★ | AD9883 采样时钟 PAL 制相位调整    |

| PHASEN  | 00 ★ | AD9883 采样时钟 NTSC 制相位调整   |

| CORE    | 10 ★ | 核化降噪控制                   |

| >> MODE |      | 1   中口年校工作 MODE 1 0 不知工口 |

注: MODE. 0: 0-上电先待机 1-上电后直接开机; MODE. 1: 0-关闭工厂调试快捷键 1-打开工厂调试快捷键; MODE. 2:0-中文/英文 1-英文; MODE. 3: 0-TCL LOGO 1-英文 LOGO; MODE. 5 MODE. 4: 搜台默认制式选择 00-D/K 01-BG 02-I

```

第4页

显示位置调整(若画面中心偏,可适当调调整对应模式参数)

YUV 模式 PAL 制场显示位置调整

YUVPISSPV

1C

YUV 模式 PAL 制行显示位置调整

YUVPISSPH

54

YUVNISSPV

YUV 模式 NTSC 制场显示位置调整

2B

YUV 模式 NTSC 制行显示位置调整

YUVNISSPH

4A

TVSPISSPV

1C

TV/AV PAL 制场显示位置调整

TVSPISSPH

7C

TV/AV PAL 制行显示位置调整

TV/AV NTSC 制场显示位置调整

TVSNISSPV

2B

TVSNISSPH

6C

TV/AV NTSV 制行显示位置调整

```

|             | 倍行板行场参数设定                                         |

|-------------|---------------------------------------------------|

| 40 ★        | N制行同步脉冲宽度设定                                       |

| 4E ★        | N制行消隐脉冲宽度设定                                       |

| B4 ★        | N 制行有效信号宽度设定                                      |

| 02 ★        | N制场同步脉冲宽度设定                                       |

| 1B ★        | N制场消隐脉冲宽度设定                                       |

| 7C ★        | N 制场有效信号宽度设定                                      |

| 40 ★        | PAL 制行同步脉冲宽度设定                                    |

| 4C ★        | PAL 制行消隐脉冲宽度设定                                    |

| B4 ★        | PAL 制行有效信号宽度设定                                    |

| 02 ★        | PAL 制场同步脉冲宽度设定                                    |

| 18 ★        | PAL 制场消隐脉冲宽度设定                                    |

| 76 <b>★</b> | PAL 制场有效信号宽度设定                                    |

|             | 4E ★ B4 ★ 02 ★ 1B ★ 7C ★ 40 ★ 4C ★ B4 ★ 02 ★ 18 ★ |

第6页

| NACQHLS  | 83 ★ | N 制采样位置设定             |

|----------|------|-----------------------|

| PACQHLS  | 83 ★ | PAL 制采样位置设定           |

| KHPW     | 04 ★ | 高通滤波器提升控制             |

| KBPW     | 04 ★ | 带通滤波器提升控制             |

| KLPW     | 04 ★ | 低通滤波器提升控制             |

| CLAMP_PL | 05 ★ | AD9883A 箝位位置调整        |

| CLAMP_DU | 05 ★ | AD9883A 箝位宽度调整        |

|          |      |                       |

| 第7页      |      |                       |

| PR-G93   | 80 ★ | 电脑模式低色温 9300K 红色驱动电平  |

| PG-G93   | 67   | 电脑模式低色温 9300K 绿色驱动电平  |

| PB-G93   | 6C   | 电脑模式低色温 9300K 蓝色驱动电平  |

| PR-C93   | 90 ★ | 电脑模式低色温 9300K 红色截止电平  |

| PG-C93   | 89   | 电脑模式低色温 9300K 绿色截止电平  |

| PB-C93   | 7E   | 电脑模式低色温 9300K 蓝色截止电平  |

| PR-G11   | 80 ★ | 电脑模式高色温 11000K 红色驱动电平 |

| PG-G11   | 69   | 电脑模式高色温 11000K 绿色驱动电平 |

| PB-G11   | 54   | 电脑模式高色温 11000K 蓝色驱动电平 |

| PR-C11   | 90 ★ | 电脑模式高色温 11000K 红色截止电平 |

| PG-C11   | 8C   | 电脑模式高色温 11000K 绿色截止电平 |

| PB-C11   | 80   | 电脑模式高色温 11000K 蓝色截止电平 |

# 四、QA 测试注意事项:

#### 1. 白平衡测试

测量白平衡时须将图像菜单中的"图像美化"设为"关闭"状态;低色温和高色温都要检测;另外,因 PDP 显示原理与 CRT 不同,全屏最大亮度较低(40-60nit),故基准白测试条件须改为用黑底白窗信号调制的射频信号(带色同步脉冲信号),视频电平为 50%,窗口亮度为 100nit 时进行测试。

# 2. 伴音参数测试

测量伴音有关参数时,须将"DBE"、"AVC"关掉,并将"音效"设为"标准"状态进行测量。

# 五、用户菜单设置的出厂设定:

整机出厂前相关设定如下:

| 图像效果         | 明亮   |

|--------------|------|

| 图像色温         | 低    |

| 图像美化         | 开启   |

| DNF(降噪)      | 模式 1 |

| AFT (自动频率跟踪) | 开启   |

| 音效           | 标准   |

| 音量           | 30   |

| AVC (智能音量控制) | 开启   |

| DBE (动态低音增强) | 开    |

| 画效 (PC)      | 图画   |

注: 以上设定及用户菜单中的其它设定的意义与操作方法请参考说明书。

# 第十章 主要元器件物料清单

| 物品代码              | 物品名称                              | 子件消耗量 | 位置      |

|-------------------|-----------------------------------|-------|---------|

| 13-000NV3-20B     | 集成块 NV320                         |       | 1U6     |

| 13-0082B7-15B     | 集成块 P82B715TD                     |       | 1U6     |

| 13-0082B7-15B     | 集成块 P82B715TD                     |       | 1U11    |

| 13-0082B7-15B     | 集成块 P82B715TD                     |       | 1U503   |

| 13-0082B7-15B     | 集成块 P82B715TD                     |       | 1U505   |

| 13-00AS12-13B     | 四合一遥控 IC AS1213B                  |       | 1IC01   |

| 13-00LA42-82S     | IC LA4282 (AUDIO O/P)             |       | 1IC601  |

| 13-024LC1-6BB     | 集成块 24LC16B                       |       | 1U502   |

| 13-0AD988-3AB     | 集成块 AD9883                        |       | 1U302   |

| 13-74HC12-5DB     | 集成块 74HC125D                      |       | 1U5     |

| 13-74HC54-1DB     | 集成块 74HC541D                      |       | 1U2     |

| 13-74HC54-1DB     | 集成块 74HC541D                      |       | 1U3     |

| 13-74HC54-1DB     | 集成块 74HC541D                      |       | 1 U4    |

| 13-74HC54-1DB     | 集成块 74HC541D                      |       | 1U5     |

| 13-88L284-AEB     | 集成块 MX88L284AEC                   |       | 1U100   |

| 13-C74LVX-14B     | 集成块 MC74LVX14                     |       | 1U506   |

| 13-D1085V-33S     | 集成块 LD1085V33                     |       | 1U2     |

| 13-DS90C3-83B     | 集成块 DS90CF383AMTD                 |       | 1U705   |

| 13-DS90CF-38B     | 集成块 DS90CF384AMTD                 |       | IU1     |

| 13-EF4052-BTB     | 集成块 HEF4052BT(D)                  |       | 1U600   |

| 13-HC4046-ADB     | 集成块 MC74HC4046AD                  |       | 1U3     |

| 13-HC4046-ADB     | 集成块 MC74HC4046AD                  |       | 1U4     |

| 12 101004 (2) (2) | 集成块 AIC1084-33CM 3.3V             |       | 17.200  |

| 13-IC1084-CMB     | (TO-263)<br>集成块 AIC1084-33CM 3.3V |       | 1U300   |

| 13-IC1084-CMB     | (TO-263)                          |       | 1U301   |

| 13-LD1117-33B     | 3.3V 稳压 IC                        |       | 1U10    |

| 13-LM431A-CZT     | 可调稳压 IC LM431ACZ(TO-92)           |       | 1Q871   |

| 13-MAX810-STB     | 集成块 MAX810STR                     |       | 1U8     |

| 13-MAX810-STB     | 集成块 MAX810STR                     |       | U501    |

| 13-MSP341-0TB     | 集成块 MSP3410G(64PINS)              |       | ICN01   |

| 13-MTV130-00B     | 集成块 MTV130                        |       | 1U601   |

| 13-P89C61-X2B     | IC MCU P89C61X2BA                 |       | 1U500   |

|                   | 视频开关 IC PI5V330Q (QSOP 封          |       |         |

| 13-PI5V33-0QB     | 装)                                |       | 1 U603  |

| 13-S16320-T6B     | 16M SGRAM HYB39S16320TQ-6         |       | 1 U7    |

| 13-SFH615-A3P     | 光耦 SFH615A3C                      |       | 1 IC802 |

| 13-SN74LV-C1P     | LOGIC IC SN74LVC1G14DCKR          |       | 1 U7    |

| 13-SN74LV-C1P     | LOGIC IC SN74LVC1G14DCKR          |       | 1U504   |

| 13-SN74LV-C1P     | LOGIC IC SN74LVC1G14DCKR          |       | 1D700   |

| 13-STRG66-53S     | 集成块 STR-G6653                     |       | 1 IC801 |

| 13-TDA875-5TB     | IC TDA8755T (A/D)                 |       | IU1     |

| 13-TDA917-8TB     | 集成块 TDA9178T                      |       | 1 IC202 |

| 13-TDA918-1TB     | 集成块 TDA9181T/N1                   |       | 1 IC203 |

| 13-TDA932-1HB | 集成块 TDA9321H-N2    | 1IC201 |

|---------------|--------------------|--------|

| 13-TV212M-32P | 集成块 MTV212M32(CPU) | 1U9    |

| 13-UA7808-C0S | 集成块 UA7808C        | 1IC101 |

| 13-V16161-0DB | 集成块 HY57V161610D   | 1U400  |

| 13-V16161-0DB | 集成块 HY57V161610D   | 1U401  |