## LCD 电视线路原理

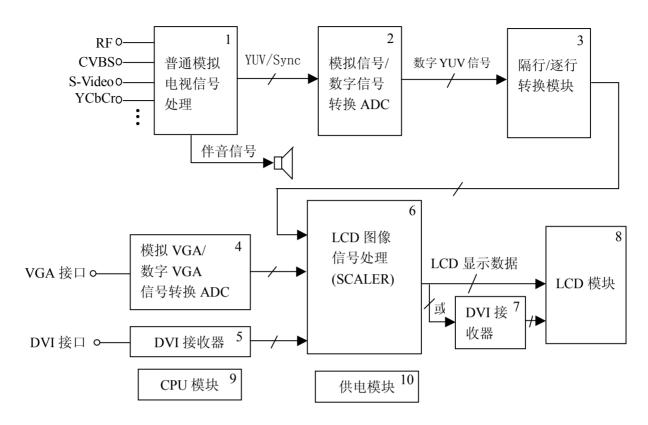

图 1: LCD 电视原理框图

LCD 电视的原理框图如上图 1 所示,主要由以下几个部分组成:

- 1、普通模拟电视信号处理模块。该模块与普通电视机中的电视信号处理部分功能相同,其可接受多种输入信号格式,如 RF 电视射频信号、CVBS 复合电视信号、S-Video 信号、色差分量信号等。 RF 电视射频信号的接收一般使用一体化二合一高频头进行处理,处理后可直接输出复合电视信号和解调的伴音信号。同时,高频头也可输出第二伴音中频信号 SIF 提供给带丽音解码的机型使用。高频头输出的复合电视信号经视频解码 IC 处理后,输出模拟 YUV(或 RGB)信号及行场同步信号供数字板进行处理使用。

- 2、模拟信号/数字信号转换模块。该模块把三通道模拟 YUV(或 RGB)信号,通过 AD 转换器处理后,转变为 24 路数字 YUV(或 RGB)信号提供给逐行处理板使用。

- 3、隔行/逐行转换模块。该模块把隔行格式的数字 YUV(或 RGB)信号进行逐行处理后输出一标准逐行格式的数字 YUV(或 RGB)信号。

- 4、模拟 VGA/数字 VGA 信号转换模块。该模块主要用把 PC 输出的标准模拟 VGA 视频信号转变成 24 位的并行数字 VGA 视频信号。

- 5、DVI 串行/并行转换模块。这部分的功能主要由 DVI 接收器来实现。其接收 PC 输出的标准串行数字视频 DVI 信号,然后将其转变为 24 位(或 48 位)并行数字视频信号。

- 6、LCD 图像处理模块 (SCALER)。该模块的核心是一个高性能的平板图像处理器,可对前端进来的多种格式数字视频信号进行处理,输出平板显示模块可接受的平板图像显示数据格式。其主要功能有:数字色度亮度处理、彩色 γ 校正、图像大小缩放、画质改善、运动补偿、边缘平滑等。

- 7、DVI 并行/串行转换模块。这部分的功能主要由 DVI 发送器来实现。其接收平板图像处

理器输出的 24 位(或 48 位)平板图像显示数据,然后将其转变为 DVI 标准的串行输出数据格式,直接连接带 DVI 输入接口的 LCD 显示模块。

- 8、LCD 显示模块。该模块是 LCD-TV 的显示终端, 其接收平板图像处理器输出的平板图像显示数据(或 DVI 格式的平板图像显示数据, 与 LCD 显示模块的输入接口有关), 经内部时序控制电路转换后驱动 LCD 屏显示出正确的视频图像。

- 9、CPU模块。提供人机接口及对电路的各个功能模块进行功能设置和控制。

- 10、供电模块。对电源接口输入的 12V 和 24V 直流电进行 DC/DC 转换后,提供系统需要的各种不同电压。

下面以 TCL LCD 电视为例,对 LCD 电视各个功能模块的线路原理进行一些具体的分析。(详细的电路原理请参照附图的 LCD-TV 线路原理图。)

#### 一、普通模拟电视信号处理模块(模拟板)

其电路原理如附图 1 所示。该模块主要由高频头 TU1、视频信号处理器 IC201 (TDA9321H)、丽音解码器 IC204(MSP3410G)、CPU微处理器 IC1(MTV212M64)、EEPROM 存储器 IC2(24C08)、动态梳状滤波器 IC203 (TDA9181T)、画质改善器 IC202 (TDA9178T)、功率放大器 IC206 (TPA1517)、电源控制器 IC802~804 (LM2596、KA278R08) 通用双运算放大器 IC205 (SL4558) 等 IC 及一些外围器件组成。

TUI 为一体化二合一高频头,内部包含了普通数字高频头功能及多制式图像伴音中频解调功能,可直接输出复合电视信号和解调的伴音信号。同时,高频头也可输出第二伴音中频信号 SIF 提供给带丽音解码的机型使用。该高频头采用单一 5V 电源供电,内含 DC/DC 转换器可把 5V 变为频率合成所需要的 33V 调谐高电压。该高频头具有集成度高、电性能好、体积小重量轻等特点,在 LCD 电视上采用,一方面可以减小系统的体积及重量,另一方面可以简化线路的设计、降低系统成本,同时也提高了系统的 TV 接收性能及可靠性。

从高频头 TU1 16 脚输出的复合视频信号 CVBS 经 R108 阻抗匹配电阻后经 C204 耦合电容后从 IC201 的 14 脚送入 IC201 内部进行处理。IC201 使用飞利浦公司生产的高端视频输入处理 IC,型号为 TDA9321H。TDA931H的内部集成了多制式图像及伴音中频解调处理功能(在本线路上没有使用)、视频输入选择开关、多制式视频信号解码及处理、YUV 输入输出接口、行场同步小信号处理等功能。

从14脚(CVBSint)进入的 TV 复合视频信号,16脚(CVBS1)进入的 AV 视频信号,18脚(CVBS2)进入的自测试图像视频信号,20脚(CVBS3/Y3)、21脚(C3)和23脚(CVBS4/Y4)、24脚(C4)进入的 S端子信号,经内部视频输入选择开关选择后,送入视频解码单元进行处理,如果选择的是复合视频信号输入,该信号经选择开关后将从26脚(COMB CVBS)输出,经 Q1 (BC847)缓冲后从 IC203的12脚(Y/CVBSI)送入 TDA9181T的内部进行 Y/C分离,分离出来的 Y和 C信号分别从 IC203的14脚(Y/CVBSI)送入 TDA9181T的内部进行视频解码。解码出来的 YUV 分量信号经内部处理后,分别从 IC201的 49脚(Yo)、50脚(Uo)和51脚(Vo)输出,从 IC201的各脚(Yin)、8脚(Uin)和9脚(Vin)进入TDA9178T的内部进行画质改善处理后,从 IC202的6脚(Yin)、8脚(Uin)和9脚(Vin)进入TDA9178T的内部进行画质改善处理后,从 IC202的19脚(Yout)、17脚(Uout)和16脚(Vout)输出,经 Q203~Q208三极管(BC847)组成的两级缓冲器缓冲后从接口 P201输出到数字板的逐行转换模块做进一步处理。IC201分离出的行场同步信号也分别从60脚(HACLP)和61脚(VA),经 P201连接到数字板的逐行转换模块。

从 TU1 出来的第二件音中频信号 SIF, 经 Q101 缓冲后,连接到 IC204(MSP3410G)的 50 脚(ANA 1+)。IC204 为多标准丽音解码 IC,可解码各种不同制式的数字伴音标准。

TU1 18 脚输出的电视伴音信号从 IC204 的 47 脚(MONOi)输入。IC204 可根据当前的伴音格式是立体声伴音或是单声道伴音而选择高频头的 SIF 为输入或 AUDIO 为输入。从 AV 输入端口来的两路音频信号分别 IC204 的 41 脚(SC2\_LI)、42 脚(SC2\_RI)和 44 脚(SC1\_LI)、45 脚(SC1\_RI)输入。IC204 根据当前的工作模式选择相应的输入通道,经内部处理后分别输出两路伴音信号。一路从 IC204 的 17 脚(DACA\_R)和 18(DACA\_L)脚输出,主要用于监听,驱动小功率耳机。另一路从 IC204 的 20 脚(DACM\_R)和 21(DACM\_L)脚输出,送入 IC206(TPA1517)进行功率放大后去推动喇叭发出声音。

IC206 为 TI 公司生产的 3W x 2 双通道立体声功率放大器 TPA1517,采用 20 脚 DIP 封装,单9.5V-18V 工作电压,工作时无需散热片,可利用电路板铜箔及自身散热,其具体应用线路如附图 1 所示。

模拟板的控制功能由 IC1(MTV212M64)来实现。IC1 为 MYSON 公司生产的 8051 内核监视器专用 CPU,内部集成 512Byte 数据 RAM、64Kbyte 程序 FLASH-ROM、AD 转换器、I<sup>2</sup>C 总线接口、自测图案发生器、行场同步信号处理器等功能。主要提供人机接口、模拟板设置及控制、与数字板通信等功能。主要管脚功能有: 43 脚和 44 脚为 VGA 行场同步输入端,26 脚和 27 脚为面板按键输入端,19 脚为红外遥控信号输入端,16 脚为 LCD 面板电源控制输出端,15 脚为内部自测试图案视频输出端,23 脚和 24 脚为 I<sup>2</sup>C 总线时钟及数据端。

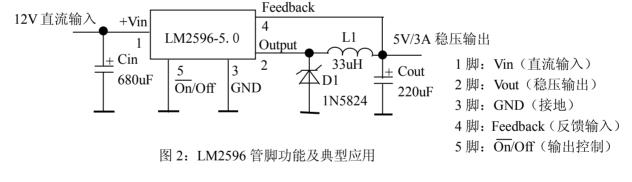

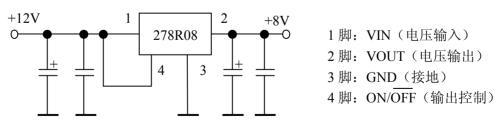

IC802~803 为 NS 公司生产的 DC/DC 转换器 IC,型号为 LM2596-xx (后面的-xx 表示输出电压,如-5.0表示 5V 输出电压),采用 5 脚 TO-220 封装或贴片 5 脚 TO-263 封装形式,主要用于把 LCD 电视外接交流适配器输入的 12V 直流电源转变为系统所需的各种不同电压,为系统提供稳定可靠及高效的电源。管脚功能及典型应用电路如图 2 所示。IC804 为 4 脚 TO-220 封装的 8V 四端稳压器,型号为 KA278R08(或其他功能相当的型号),其管脚功能及典型应用如图 3 所示。

图 3: 278R08 管脚功能及典型应用

### 二、逐行转换处理模块

这部分线路原理如附图 2~5 所示。具体功能的实现主要由 U3(AD9883)和 U6(FLI2200)两块 IC 组成。AD9883 是 ADI 公司专为平板显示模拟前端接口设计的模数转换集成电路,

采用 80 脚 LQFP 封装,单一 3.3V 供电电压,内置三通道 8 位 140MHz 采样频率 AD 转换器,可输出 4:2:2 标准的数字视频格式。

从模拟板过来的 YUV 三路模拟色差分量信号,经阻抗匹配和低通滤波去掉高频干扰成分后,分别从 AD9883 的 48、43 和 54 脚耦合进 AD9883 内部,经 3 通道 AD 转换器转换后分别从 AD9883 的 2~9 脚、12~19 脚和 70~77 脚输出 4:2:2 格式的 YUV 数字视频信号。从模拟板过来的行同步信号(HSYNC)和场同步信号(VSYNC)经 U2(74LVC14)缓冲及电平转换后,分别从 30 脚(HSYNC)和 31 脚(VSYNC)从送入 AD9883 的内部,经内部PLL 环路控制后,产生内部工作所需的时钟信号及与输出数据对应的数据同步时钟信号(U3 的 67 脚:DATACK)和行同步信号(U3 的 66 脚:HSOUT)、场同步信号(U3 的 64 脚:VSOUT)。

U3 输出的数字格式 YUV 信号及同步信号分别从 U6 的 20~27 脚(Y 分量输入)、8~15 脚(U 分量输入)、30~39 脚(V 分量输入)、40 脚(数据同步信号)、3 脚(行同步信号)和 4 脚(场同步信号)输入,经 U6 内部逐行转换、画质改善、运动补偿及边缘平滑等处理后,从 U6 的 65~72 脚和 93~102 脚输出 16 位数据格式的逐行 YUV 数字信号,U6 的 89~92 脚和 117 脚输出对应的各种同步时钟信号。

U6 采用 GENESIS MICROCHIP 公司生产的数字视频去隔行处理芯片 FLI2200,内含多种画质改善功能,可支持 525 行 60Hz NTSC 或 625 行 50Hz PAL/SECAM 制式信号输入,可自动检测输入视频信号的制式,支持多种逐行输出数据格式(8/10/16/20 位 YUV 或 24/30位 YPbPr/RGBHV),内含 SDRAM 控制器(可在外部连接 2M x 32bit SDRAM),内置两线  $I^2$ C 总线接口,内置时钟发生器及显示时序发生器等功能部件。

FLI2200 采用 176 脚 TQFP 封装, 3. 3V 和 2. 5V 双电压供电。其具体得外围电路连接及外部 SDRAM 连接如附图 3~5 所示。

#### 三、VGA 接口模块

VGA 接口主要处理 PC 输出的标准 VGA 信号,包括模拟 VGA 信号和数字 VGA 信号两部分。

### 1、模拟 VGA 接口

模拟 VGA 接口的具体线路如附图 6、附图 7 和附图 10 所示。这部分主要由 U11 芯片的模拟接口部分及一些外围元器件组成。

U11 的型号为 JAG ASM, 这是 GENESIS MICROCHIP 公司开发的一片高集成度、功能强大的平板图像处理芯片。其采用 388 脚 BGA 封装, 3.3V 和 2.5V 双电压供电。内部集成了功能强大的平板图像缩放处理器(SCALER)、5 路独立的输入前端(两路模拟输入接口,两路数字输入接口,一路 16 位视频信号输入接口)、3 通道 8 位 135MHz ADC、SDRAM 控制器、PLL 时钟控制器及一些画质改善功能增强等功模块。

JAG ASM 内部集成了 3 通道 8 位 135MHz ADC,因此其可和模拟输入直接连接,其提供的两路模拟输入接口可同时输入两路模拟 VGA 信号。本设计只使用了一路模拟输入接口来连接一路模拟 VGA 信号输入。从标准 15 针 VGA 接口(DB15)进来的 RGB 三路模拟信号经阻抗匹配及低通滤波后,分别从 U11 的模拟信号输入接口(A12 脚:R1N、A13 脚:R1P、A16 脚:G1N、A17 脚:G1P、A20 脚:B1N 和 A21 脚:B1P)输入到 U11 的内部,经内部 AD 转换器转化为 24 位数字 RGB 信号后,再送入 LCD 图像处理器进行相应的处理。

#### 2、数字 VGA 接口(为可选部分,在有 DVI 输入接口的机型才有)

数字 VGA 接口的具体线路如附图 10 和附图 16 所示。这部分主要由 DVI 接收芯片 U36 (SiI161) 和 U11 的数字接口部分及一些外围元器件组成。

SiI161 是 Silicon Image 公司生产的平板连接数字接收器,该芯片使用了 Silicon Image 公司的 PanelLink 数字技术,可支持 VGA 到 UXGA (可选带宽 25-162MHz),兼容 DVI1.0

接口标准,支持24位16.7M真彩色,支持1像素/时钟或2像素/时钟24位或48位输出格式。

SiI161 采用 100 脚 TQFP 封装,单一 3. 3V 供电电压。具体线路连接如附图 16 所示。 四、LCD 图像处理模块 (SCALER)

TCL LCD-TV 的 LCD 图像处理模块主要是基于 GENESIS MICROCHIP 公司 JAG ASM 芯片(在电路图上的标号为 U11)的一个具体实现方案。除了上面所述有关 U11 的模拟及 数字接口功能外,U11 还提供多个接口来连接不同的功能输入,来支持构成一个功能强大的 LCD 平板显示控制处理方案。

#### 1、SDARM 接口

U11 内置一个 SDRAM 接口,可与标准的 SDRAM 芯片提供无缝连接。U11 与 SDRAM 芯片的连接如附图 8 和附图 9 所示。附图 9 中的 U12 和 U13 为两片容量为 2M x 32bit 的 SDRAM 芯片,型号为 K4S643232C(或其他功能相同的标准 SDARM 芯片型号),采用 86 脚标准 TSOP II 封装,3.3V 供电电压,输入输出符合 LVTTL 电平标准。两片 SDRAM 芯片并联连接,构成 2M x 64bit 结构,为 U11 提供容量为 16MB 的数据 RAM 供图像数据处理及帧数据缓冲使用。

#### 2、数字视频输入接口。

U11 提供两个 24 位数字视频输入接口,可以同时连接两个 24 位 DVI 兼容数字视频输出或 1 个 48 位 DVI 兼容数字视频输出。本设计只使用了一路 24 位数字视频输入接口。从 DVI 接收器芯片(U36: SiI161)输出的 24 位数字视频信号经保护电阻后直接送入 U11 的数字视频输入口 PA(PA00~PA23),供 U11 内部的 LCD 图像处理器处理。

#### 3、视频信号输入接口

U11 内置一个独立的 16 位视频信号输入接口,可提供与视频解码器输出或 MPEG2 解码器输出等标准输出视频格式的直接连接。

在本设计中,视频信号输入接口连接 U6 (FLI2200)输出的经过去隔行处理后的标准 16 位逐行格式视频信号。具体的线路连接如附图 4 和附图 10 所示。

### 4、LCD 显示接口

这部分的具体线路如附图 11~附图 13 所示。U11 在 CPU 的控制下从各个接口输入的信号中选择一路,然后送到内置的 LCD 图像处理器中进行处理(主要包括画质处理、格式变换、大小缩放、时序变换等)。经过内部的一系列处理后,数字视频信号被变换为符合 LCD 平板显示的数据格式及时序,从 U11 的平板显示接口输出 48 位(或 36/24 位/18 位,具体的位数视 LCD 平板模块的输入接口而定,由 CPU 控制 U11 选择)平板显示数据和 4 路同步控制信号。

U11 平板显示输出接口可直接连接标准 48 位或 24 位并行显示数据输入模式的 LCD 模块,对于支持 LVDS 信号输入的 LCD 模块,U11 平板显示输出接口输出的数据及同步控制信号则要经过转换后才能与带 LVDS 输入的 LCD 模块连接,这个转换功能由 DVI 发送器芯片来实现。

由 U11 输出的 24 位平板显示数据及 4 路同步信号送入 U15 进行格式转换。U15 采用 TI 公司的平板连接发送器芯片,型号为 SN75LVDS83,56 脚 TSOP 封装,3.3V 单供电电压,时钟频率从 31MHz-68MHz,支持 SVGA 到 SXGA 格式,提供28 路并行输入4路 LVDS 输出。转换后的4路 LVDS 信号分别从U15的47 脚(Y0P)和48 脚(Y0M)、45 脚(Y1P)和46 脚(Y1M)、41 脚(Y2P)和42 脚(Y2M)、37 脚(Y3P)和38 脚(Y3M)、39 脚(CLKOUTP)和40 脚(CLKOUTM)输出。这部分的电路原理如附图13所示。

#### 5、CPU接口

U11 通过一个 8 位的并行接口与外部 CPU 连接,为了减少管脚,接口采用分时复用模

式,低 8 位地址与数据复用一个 8 位口(MCAD0~7)。U11 与 CPU 连接的其他管较为: MCA8、MCA9:与 CPU 连接的第 8 和第 9 位地址线,MCALE:高电平有效地址锁存信号输入,MCRD#:低电平有效读控制信号输入,MCWR#:低电平有效写控制信号输入,INTR#:低电平有效中断请求输出。具体线路如附图 10 和附图 14 所示。五、LCD 模块

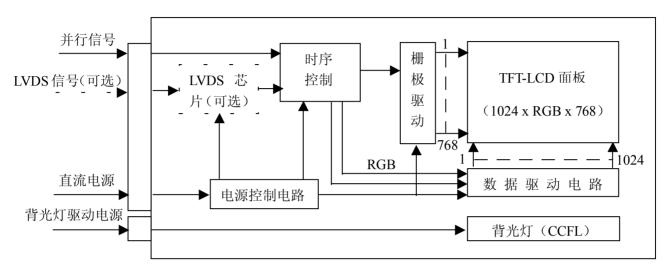

图 4: LCD 模块内部组成原理框图

TCL的 LCD 电视采用专为 LCD-TV 开发的有源矩阵 TFT-LCD 显示屏模块,具有亮度更高、对比度更大、视角更宽、响应速度更快、分辨率更高(液晶屏幕的最佳分辨率一般可达 1024X768,较传统电视 300~500 线的分辨率,具有更高的清晰度)、寿命更长、色彩丰富(该屏拥有 16.7 百万的色彩,画面层次分明,颜色绚丽真实)等特点。其内部原理框图如图 4 所示。

#### 六、CPU 及供电模块

LCD 电视 CPU 及供电部分的线路原理如附图 14 及附图 15 所示,其具体线路原理与普通电视上的大体相同,提供整个系统的功能控制及电源供给。

# 附: IC 引脚功能

# 1、AD9883 引脚功

| I/O       | 符号                                                                  | 功能说明                                                                                                 | 电压值                                                                                                                                                      | 引脚                                                                                                                                                                               |

|-----------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 新入<br>输出  | RAIN GAIN BAIN HSYNC VSYNC SOGIN CLAMP COAST  Red [7:0] Green [7:0] | 功能说明 R 模拟转换输入 G 模拟转换输入 B 模拟转换输入 行同步输入 场同步输入 场同步输入 G 信号附加同步输入 钳位输入(外部钳位信号) PLL COAST 输入 R 转换输出 G 转换输出 | 0.0 V to 1.0 V<br>0.0 V to 1.0 V<br>0.0 V to 1.0 V<br>3.3 V CMOS<br>3.3 V CMOS<br>0.0 V to 1.0 V<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS | 54<br>48<br>43<br>30<br>31<br>49<br>38<br>29<br>70–77<br>2–9                                                                                                                     |

| 参考        | Blue [7:0] DATACK HSOUT VSOUT SOGOUT  REF BYPASS MIDSCV             | B转换输出<br>数据时钟输出<br>行同步输出<br>场同步输出<br>场信号附加同步输出<br>内部参考电压旁路<br>内部中点电压旁路                               | 3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS                                                                                       | 12–19<br>67<br>66<br>64<br>65<br>58<br>37                                                                                                                                        |

| /// . / . | FILT                                                                | PLL环路滤波                                                                                              | 227                                                                                                                                                      | 33                                                                                                                                                                               |

| 供电        | Vdd<br>Vdd<br>PVd<br>GND                                            | 模拟部分供电数字输出部分供电PLL部分供电接地                                                                              | 3.3 V<br>3.3 V<br>3.3 V<br>0 V                                                                                                                           | 39, 42,<br>45, 46, 51, 52,<br>59, 62<br>11, 22, 23, 69,<br>78, 79<br>26, 27, 34, 35<br>1, 10, 20, 21,<br>24, 25, 28, 32,<br>36, 40, 41, 44,<br>47, 50, 53, 60,<br>61, 63, 68, 80 |

| 控制        | SDA<br>SCL<br>A0                                                    | I2C 总线数据线<br>I2C 总线时钟线<br>I2C 接口地址输入 1                                                               | 3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS                                                                                                                   | 57<br>56<br>55                                                                                                                                                                   |

# 2、FLI2200 引脚功能

| 211 | 2、112200   |               |                          |                                                                                                            |  |  |  |

|-----|------------|---------------|--------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| I/O | 符号         | 功能说明          | 电压值                      | 引脚                                                                                                         |  |  |  |

| 供电  | Vss        | 数字部分接地脚       | 0 V                      | 2, 17, 34, 55, 64, 74, 85,96, 106, 115, 124, 132, 138, 145, 152, 159, 168 1, 33, 63, 73, 84, 95, 105, 114, |  |  |  |

|     | VDD33      | 数字部分供电        | 3.3 V                    | 123, 137, 144,151, 167<br>16, 54, 107, 158<br>43                                                           |  |  |  |

|     | VDD25      | -<br>内核逻辑部分供电 | 2.5 V                    | 42                                                                                                         |  |  |  |

|     | AVss       | PLL 部分接地      | 0 V                      |                                                                                                            |  |  |  |

|     | AVDD       | PLL 部分供电      | 2.5 V                    |                                                                                                            |  |  |  |

| 控   | RESETB     | 内部复位控制输入      | 3.3 V CMOS               | 49                                                                                                         |  |  |  |

| 制   | OE         | 输出允许控制        | 3.3 V CMOS               | 53                                                                                                         |  |  |  |

|     | IFORMAT2-0 | 输入信号格式控制      | 3.3 V CMOS<br>3.3 V CMOS | 56-58                                                                                                      |  |  |  |

|     | OFORMAT2-0 |               | J.J V CIVIOS             | 59-61                                                                                                      |  |  |  |

|                         | DADDR1-0<br>MODE<br>SDA<br>SCL<br>PIXCLK<br>N/P/IN/OUT<br>NOMEM                   | 输出信号格式控制 I2C 总线地址设置 I2C 总线操作模式控制 I2C 总线操作模式控制 I2C 总线数据线 I2C 总线时钟线 像素时钟输入 制式指示 无存储器模式控制输入                                                           | 3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS                                                         | 44-45<br>46<br>47<br>48<br>40<br>62<br>52                                                             |

|-------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 输入                      | G/YIN9-0<br>B/CbIN9-0<br>R/CrIN9-0<br>HSYNCREFI<br>VSYNCREFI<br>FLDIN             | 10 位 G 信号或 Y 信号输入<br>10 位 B 信号或 Cb 色度信号输入<br>10 位 R 信号或 Cr 色度信号输入<br>行同步参考输入<br>场同步参考输入<br>场识别信号输入                                                 | 3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS                                                                       | 27-18<br>15-6<br>39-35,32-28<br>3<br>4<br>5                                                           |

| 输出                      | G/YOUT9-0 B/CbOUT9-0 R/CrOUT9-0 CCLKO YCLKO VREFO HREFO VSYNC/CREFO H/CSYNCO FILM | 10位 G 信号或 Y 信号输出<br>10位 B 信号或 Cb 色度信号输出<br>10位 R 信号或 Cr 色度信号输出<br>色度采样时钟输出<br>亮度采样时钟输出<br>有效场开始指示输出<br>有效行开始指示输出<br>行同步参考输出<br>场同步参考输出<br>电影模式检测输出 | 3.3 V CMOS<br>3.3 V CMOS | 65-72, 75-76<br>93-94, 97-104<br>77-83, 86-88<br>116<br>117<br>89<br>90<br>91                         |

| SD<br>RA<br>M<br>控<br>制 | ADDR10-0<br>DATA29-0<br>MEMCLKO<br>WEN<br>RASN<br>CASN<br>BSEL                    | SDRAM 地址线<br>SDRAM 数据线<br>SDRAM 时钟<br>SDRAM 写控制<br>SDRAM 行地址选通<br>SDRAM 列地址选通<br>SDRAM 块选择                                                         | 3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS                                                         | 125-131, 133-136<br>176-169, 166-160, 157-153,<br>150-146, 143-139<br>118<br>119<br>120<br>121<br>122 |

| 测<br>试                  | TEST5-0<br>TESTO1-0                                                               | 测试信号输入<br>测试信号输出                                                                                                                                   | 3.3 V CMOS<br>3.3 V CMOS                                                                                                                               | 41, 50, 51, 108, 109, 111<br>112, 113                                                                 |

# 3、JAG ASM 主要管脚功能

| I/O     | 符号                                                       | 功能说明                                                                                                                                        | 电压值                                                                                                                        | 引脚                                                                                           |

|---------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| ADC&PLL | R1P R1N G1P G1N B1P B1N R2P R2N G2P G2N B2P B2N Xin Xout | 通道1模拟R正输入<br>通道1模拟R负输入<br>通道1模拟G页输入<br>通道1模拟B正输入<br>通道1模拟B页输入<br>通道2模拟R正输入<br>通道2模拟R页输入<br>通道2模拟R页输入<br>通道2模拟R页输入<br>通道2模拟R页输入<br>通道2模拟R页输入 | 0.7 / 1.0 V<br>0V<br>0.7 / 1.0 V<br>0V | A13<br>A12<br>A11<br>A10<br>A17<br>A16<br>A15<br>A14<br>A21<br>A20<br>A19<br>A18<br>A6<br>A7 |

|               |                                       | 日长炒)               |                          |                     |

|---------------|---------------------------------------|--------------------|--------------------------|---------------------|

|               |                                       | 晶振输入<br>目标 14.11   |                          |                     |

| A D C O D I I | D) (00                                | 晶振输出               | 0.17                     | D40                 |

| ADC&PLL       | DVSS                                  | ADC 数字地            | 0 V                      | B10                 |

| 供电            | IVSS2                                 | 仪器通道数字地            | 0 V                      | B11                 |

|               | IVSS1                                 | 仪器通道模拟地            | 0 V                      | B12                 |

|               | RVSS2                                 | R数字地               | 0 V                      | B13                 |

|               | RVSS1                                 | R模拟地               | 0 V                      | B14                 |

|               | GVSS2                                 | G数字地               | 0 V                      | B15                 |

|               | GVSS1                                 |                    | 0 V                      | B16                 |

|               | BVSS2                                 | G模拟地               | 0 V                      | A17                 |

|               | BVSS1                                 | B数字地               | 0 V                      | A18                 |

|               | SVSS                                  | B模拟地               | 0 V                      | B19                 |

|               | AVSS2                                 | 参考电压地              | 0 V                      | C7                  |

|               | AVDD3                                 | I/O 地              | 2.5V                     | C8                  |

|               | AVDD4                                 | PLL 电源             | 2.5V                     | C9                  |

|               | AVDD1                                 |                    | 2.5V                     | C10                 |

|               | AVDD2                                 | PLL 电源             | 2.5V                     | C11                 |

|               | AVSS1                                 | ESD 电源             | 0 V                      | C20                 |

|               | XVDD                                  | ESD 电源             | 2.5V                     | D7                  |

|               | CVDD2                                 | 接地                 | 2.5V                     | D8                  |

|               | CVDD1                                 | I/O 供电             | 2.5V                     | D9                  |

|               | DVDD                                  | CPLL 供电            | 2.5V                     | D10                 |

|               | IVDD2                                 |                    | 2.5V                     | D11                 |

|               | IVDD1                                 | CPLL 振荡器供电         | 2.5V                     | D12                 |

|               | RVDD2                                 | ADC 数字电源           | 2.5V                     | D13                 |

|               | RVDD1                                 | 仪器数字电源             | 2.5V                     | D14                 |

|               | GVDD2                                 | 仪器模拟电源             | 2.5V                     | D15                 |

|               | GVDD1                                 | R数字电源              | 2.5V                     | D16                 |

|               | BVDD2                                 | R模拟电源              | 2.5V                     | D17                 |

|               | BVDD1                                 | G数字电源              | 2.5V                     | D18                 |

|               | SVDD                                  |                    | 2.5V                     | D19                 |

|               | PVDD1                                 | G模拟电源              | 2.5V                     | D20                 |

|               | ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' | B数字电源              | 2.00                     | D20                 |

|               |                                       | B模拟电源              |                          |                     |

|               |                                       | 内部参考电压电源           |                          |                     |

|               |                                       | PLL1 电源            |                          |                     |

| CPU 接口        | PWM1/GPIO1                            | 通用 I/O             | 3.3 V CMOS               | B1                  |

| CI U 按 II     | PWM0/GPO0/SCDT                        | 通用输出               | 3.3 V CMOS               | E2                  |

|               | PLLCLKOUT/GPIO4                       |                    | 3.3 V CMOS               | B2                  |

|               | SDATA                                 | PLL 时钟输出/通用 I/O    | 3.3 V CMOS               | F4                  |

|               | SCLK                                  | I2C 总线数据           | 3.3 V CMOS               | F3                  |

|               | MCWR#                                 | I2C 总线时钟           | 3.3 V CMOS               | E4                  |

|               | MCRD#                                 | CPU 写控制            | 3.3 V CMOS               | E3                  |

|               | MCCS#                                 | CPU 读控制            | 3.3 V CMOS               | C4                  |

|               | MCRESET#                              | 片选                 | 3.3 V CMOS               | E1                  |

|               | MCINT                                 |                    | 3.3 V CMOS<br>3.3 V CMOS | D2                  |

|               | MCALE                                 | 系统复位               | 3.5 V CIVIOS             | D3                  |

|               | MCAD0-MCAD7                           | CPU 中断请求           |                          | B6, B5, C5, D5, A4, |

|               |                                       | CPU 地址锁存           |                          | B4, A3, B3          |

|               | MCAD8                                 | 8 位 CPU 数据/地址线     |                          | C3                  |

|               | MCAD9                                 |                    |                          | A2                  |

|               |                                       | CPU 地址线 A8         |                          |                     |

|               |                                       | CPU 地址线 A9         |                          |                     |

| ÷π □          | PACLK                                 | -                  |                          | G4                  |

| 端口            | PACLK<br>PARHS/PADE                   | 端口A时钟输入            |                          | G4<br>  F1          |

|               | PARHS/PADE<br>PAHSYNC                 | 端口 A 行同步/端口 A 显示控制 |                          | F1<br>  F2          |

|               | PARSTNC                               | 端口A行同步             |                          | G3                  |

|               | AVOING                                | 端口A场同步             |                          |                     |

|               | L                                     |                    | 1                        | 1                   |

|          | T D 4 0 0 D : 0 0                                                                                                                                                         | Lynn,                                                                                                                                                                                         | l = , = _ · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | PA00-PA23                                                                                                                                                                 | 端口 A 24 位数据输入                                                                                                                                                                                 | P1, P2, N2, N3,<br>M1-M4, L1-L4, J1-J4,                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | PBCLK PBRHS/PBDE PBHSYNC PBVSYNC PB00-PB23  PCCLK PCHSYNC PCHREF PCVSYNC PC00-PC15  PCVREF/ GPIO2 PCFIELD/ GPIO3 PNLCLK PSHFCLK PDE PHSYNC PVSYNC PENVDD PENBKL PD00-PD47 | 端口 A 时钟输入<br>端口 B 行同步<br>端口 B 场间步<br>端口 B 24 位数据输入<br>端坝频解码器 16 位数据输入<br>视频解解码器 16 位数据输入<br>视频解码器 16 位数据输入<br>视频解码器 16 位数据输入<br>视频解码器 M I/O<br>显板移示形的 型型 平板显示示的 制出<br>平板显示示的 制<br>背光位平板显示数据输出 | M1-M4, L1-L4, J1-J4, H1-H3, G1, G2 P4 D6 C6 P3 AA2, AA3, Y1-Y3, W1-W4, V1-V4, U1-U4, T1-T4, R1-R3 AA4 AB3 AB2 AB1 AF1-AF4, AE1-AE4, AD1-AD4, AC1-AC4 AD5 AE5 AF12 AC13 AF20 AE21 AC21 AC21 AD21 AF22 AD13, AE13, AD14, AE14, AF14, AC15, AD15, AE15, AF15, AF15, AC16, AD16, AE16, AD17, AE17, AF17, AC18, AD18, AE18, AF18, AC19, AD19, AE19, AD20, AE20, AF5, AC6, AD6, AE6, AF6, AC7, AD7, AE7, AF7, AD8, AE8, AC9, AD9, PAE9, AF9, AC10, AD10, AE10, PD41, AD11, AE11, |

|          |                                                                                                                                                                           |                                                                                                                                                                                               | AF11, AC12, AD12,<br>AE12                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SDRAM 接口 | SDD0-SDD63 SDA0-SDA10 SDCAS# SDWE# SDRAS# SDCKO SDCKON MEMCLK SDCKE SDCKFB SDCS0# BANK DQM DQS                                                                            | 64 位 SDRAM 数据线 11 位 SDRAM 地址线 SDRAM CAS# SDRAM WE# SDRAM RAS# SDRAM 时钟 SDRAM 时钟 存储器时钟输入 SDRAM 时钟允许 SDRAM 时钟允许 SDRAM 时钟允许 SDRAM 时钟反馈 SDRAM 片选 SDRAM BANK 地址                                    | T26 R25 P24 R23 P23 T24 R24 T25 M26 M24 M23 M25                                                                                                                                                                                                                                                                                                                                                                                                                            |

更多彩电维修资料请到《彩电维修资料网》http://www.tv160.com 查询!

|  | SDRAM DQM   |  |

|--|-------------|--|

|  | DDR SDRAM 用 |  |